สารบัญ:

- ขั้นตอนที่ 1: บล็อกไดอะแกรม

- ขั้นตอนที่ 2: หลักการทำงาน

- ขั้นตอนที่ 3: การใช้งานลอจิก

- ขั้นตอนที่ 4: การแก้ไขการหยุดชะงัก

- ขั้นตอนที่ 5: การกำหนดค่าอุปกรณ์ - Matrix0 Circuit

- ขั้นตอนที่ 6: การกำหนดค่าอุปกรณ์ - SPI Clocking Logic

- ขั้นตอนที่ 7: การกำหนดค่าอุปกรณ์ - คุณสมบัติคอมโพเนนต์ Matrix0

- ขั้นตอนที่ 8: การกำหนดค่าอุปกรณ์ - วงจร Matrix1

- ขั้นตอนที่ 9: การกำหนดค่าอุปกรณ์ - ตัวนับไบนารี 3 บิต

- ขั้นตอนที่ 10: การกำหนดค่าอุปกรณ์ - ตรรกะเปรียบเทียบ 3 บิต

- ขั้นตอนที่ 11: การกำหนดค่าอุปกรณ์ - ลอจิกเปรียบเทียบดิจิทัลและการลงทะเบียนชั่วคราว

- ขั้นตอนที่ 12: การกำหนดค่าอุปกรณ์ - คุณสมบัติคอมโพเนนต์ Matrix1

- ขั้นตอนที่ 13: ผลลัพธ์

- ผู้เขียน John Day day@howwhatproduce.com.

- Public 2024-01-30 13:03.

- แก้ไขล่าสุด 2025-01-23 15:12.

ระบบควบคุมและอุปกรณ์ที่เกี่ยวข้องจัดการกับแหล่งพลังงานหลายแหล่ง เช่น สายไบแอสหรือแบตเตอรี่ และต้องติดตามสายสูงสุด (หรือต่ำสุด) ในชุดที่กำหนด

ตัวอย่างเช่น การสลับโหลดในระบบที่ขับเคลื่อนด้วย "แบตเตอรี่หลายก้อน" ต้องการให้ระบบตรวจสอบแรงดันไฟฟ้าต่ำสุดหรือสูงสุดระหว่างอาร์เรย์แบตเตอรี่ (สูงสุดหรือต่ำสุดตามฟังก์ชันของอัลกอริธึมการสลับเฉพาะ) และกำหนดเส้นทางโหลดแบบไดนามิกไปยัง แหล่งที่มาที่เหมาะสมที่สุดในแบบเรียลไทม์ หรือระบบอาจต้องยกเลิกการเชื่อมต่อแบตเตอรี่แรงดันต่ำที่สุดชั่วคราวเพื่อการชาร์จที่เหมาะสม

อีกตัวอย่างหนึ่งคือระบบพลังงานแสงอาทิตย์ที่ทันสมัย ซึ่งแผงโซลาร์เซลล์ทุกแผงมีกลไกการเอียงและวงจรติดตามแสงอาทิตย์ (ส่วนหลังให้ข้อมูลตำแหน่งดวงอาทิตย์เพื่อปรับทิศทางแผง) ด้วยข้อมูลแรงดันไฟฟ้าสูงสุด ตำแหน่งของแผงโซลาร์เซลล์แต่ละตำแหน่งสามารถปรับได้อย่างละเอียดโดยอิงจากแผงสายไฟที่ให้แรงดันเอาต์พุตสูงสุดจริง ดังนั้นจึงบรรลุระดับการเพิ่มประสิทธิภาพพลังงานที่เหนือกว่า

IC เชิงพาณิชย์มีหลายยี่ห้อ (ส่วนใหญ่เป็นไมโครคอนโทรลเลอร์) ซึ่งโดยหลักการแล้วสามารถใช้ตัวติดตามแรงดันไฟฟ้าสูงสุดได้ อย่างไรก็ตาม พวกเขาต้องการการตั้งโปรแกรมและคุ้มค่าน้อยกว่าโซลูชันสัญญาณผสม การเสริมการออกแบบ Dialog GreenPAKTM สามารถส่งผลในเชิงบวกต่อความสามารถในการจ่ายได้ ขนาด และความเป็นโมดูลของการออกแบบ การออกแบบนี้ใช้ประโยชน์จากการรวมวงจรแอนะล็อกและดิจิตอลไว้ในชิปตัวเดียว

ในคำแนะนำนี้ แอนะล็อกฟรอนต์เอนด์และลอจิกดิจิทัลที่จำเป็นในการติดตั้งตัวค้นหาแรงดันไฟฟ้าสูงสุด (หรือต่ำสุดในที่สุด) ระหว่างแหล่งกำเนิดที่แตกต่างกันแปดแหล่ง

ในการติดตั้งมอนิเตอร์แรงดันไฟสูงสุด/นาทีอนาล็อกแบบ 8 ช่องสัญญาณ SLG46620G จะถูกใช้

ด้านล่างนี้ เราได้อธิบายขั้นตอนที่จำเป็น ทำความเข้าใจวิธีการแก้ปัญหาที่ได้รับการตั้งโปรแกรมเพื่อสร้างจอภาพแรงดันไฟสูงสุด/นาทีแบบอะนาล็อก 8 ช่องสัญญาณ อย่างไรก็ตาม หากคุณต้องการเพียงแค่ผลลัพธ์ของการเขียนโปรแกรม ให้ดาวน์โหลดซอฟต์แวร์ GreenPAK เพื่อดูไฟล์การออกแบบ GreenPAK ที่เสร็จสมบูรณ์แล้ว เสียบ GreenPAK Development Kit เข้ากับคอมพิวเตอร์ของคุณและกดโปรแกรมเพื่อสร้างจอภาพแรงดันไฟสูงสุด/นาทีแบบอะนาล็อก 8 ช่อง

ขั้นตอนที่ 1: บล็อกไดอะแกรม

รูปที่ 1 แสดงไดอะแกรมส่วนกลางของระบบที่นำไปใช้

สตริงของแหล่งจ่ายแรงดันไฟที่แปรผันได้มากถึง 8 แหล่งจะถูกมัลติเพล็กซ์และเชื่อมต่อกับโมดูล ADC ของ GreenPAK ที่เชื่อมต่อกับการออกแบบภายในที่ปรับแต่งเองได้ ซึ่งสามารถเลือกแหล่งที่มีแรงดันไฟฟ้าสูงสุดเมื่อเทียบกับส่วนอื่นๆ ตรรกะภายในจะแสดงผลข้อมูลนี้สำหรับการแสดงผลหรือการประมวลผลเพิ่มเติม

การออกแบบนี้ใช้ผลิตภัณฑ์ GreenPAK SLG46620G เนื่องจากได้ฝังบล็อกการสร้างแบบแอนะล็อกและดิจิทัลที่จำเป็นทั้งหมดสำหรับแอปพลิเคชัน ในการดำเนินการนี้ อาร์เรย์จะถูกสแกนโดยใช้มัลติเพล็กเซอร์แบบอะนาล็อก ADG508 ที่ขับเคลื่อนโดย GreenPAK IC โดยตรง

ข้อมูลเอาต์พุตเป็นตัวเลขดิจิตอล 3 บิตที่สอดคล้องกับหมายเลขแหล่งจ่ายแรงดันที่แรงดันไฟสูงสุด วิธีรับข้อมูลโดยตรงคือการแสดงตัวเลขโดยใช้จอแสดงผล 7 ส่วน สามารถทำได้โดยง่ายโดยการเชื่อมต่อเอาท์พุตดิจิตอลของ SLG46620G กับไดรเวอร์การแสดงผล 7 ส่วน เช่น โซลูชัน GreenPAK ที่อธิบายไว้ใน ข้อมูลอ้างอิง หรือไอซี 74LS47 ทั่วไป

วงจรที่นำเสนอจะมองหาแรงดันไฟฟ้าสูงสุด ในการแปลงการออกแบบเป็นตัวค้นหาแรงดันไฟฟ้าขั้นต่ำ ต้องเพิ่มวงจรปรับสภาพอย่างง่ายระหว่างมัลติเพล็กเซอร์แบบอะนาล็อกและอินพุตอนาล็อก GreenPAK โดยลบเอาต์พุตมัลติเพล็กเซอร์ออกจากแรงดันอ้างอิง 1 V

ขั้นตอนที่ 2: หลักการทำงาน

การออกแบบมีจุดมุ่งหมายเพื่อเลือกแหล่งกำเนิดที่มีแรงดันไฟฟ้าสูงสุด ดังนั้นจะทำการสแกนทั้งอาร์เรย์ในขณะที่จัดเก็บค่าสูงสุดล่าสุดและเปรียบเทียบกับค่าถัดไปในอินพุต (ซึ่งเป็นของแหล่งกำเนิดแรงดันไฟฟ้าถัดไปในการสแกน)

ต่อไปนี้ เราจะอ้างอิงถึงลำดับมัลติเพล็กซ์ที่สมบูรณ์ตามอินพุตทั้งหมดว่าเป็น "สแกน" หรือ "วนซ้ำ"

การเปรียบเทียบระหว่างสองค่าไม่สามารถทำได้โดยใช้ส่วนประกอบ ACMP (อย่างไรก็ตาม มีอยู่ใน SLG46620G) แต่ใช้โมดูล DCMP เมื่อค่าต่างๆ ถูกแปลงเป็นดิจิทัลตามลำดับ นี่เป็นเทคนิคขั้นสูงและประณีตซึ่งกล่าวถึงครั้งแรกในเอกสารอ้างอิง

รูปที่ 2 แสดงให้เห็นว่า SLG46620G มีโครงสร้างอย่างไรสำหรับการออกแบบนี้

สัญญาณอินพุตแบบอะนาล็อกจะไปยังอินพุต ADC ผ่านส่วนประกอบ PGA โดยมีอัตราขยายเป็น 1 ที่ตั้งไว้ นอกจากนี้ยังสามารถตั้งค่าเกนต่างๆ ให้เหมาะสมที่สุดกับอุปกรณ์อิเล็กทรอนิกส์ปรับสภาพส่วนหน้าที่ใช้สำหรับการแมปแรงดันไฟฟ้าขาเข้ากับ 0-1 V ช่วงของโมดูล GreenPAK ADC

ADC ทำงานในโหมดปลายเดียวและแปลงสัญญาณแอนะล็อกเป็นรหัสดิจิทัล 8 บิต จากนั้นจึงโอนไปยังโมดูล DCMP รหัสดิจิทัลยังถูกป้อนเข้าไปในบล็อก SPI ซึ่งกำหนดค่าเป็นบัฟเฟอร์ ADC/FSM ซึ่งสามารถจัดเก็บรหัสดิจิทัลได้และจะไม่เปลี่ยนแปลงจนกว่าพัลส์ถัดไปจะมาถึงอินพุต SPI CLK โปรดสังเกตว่าบล็อกลอจิกเฉพาะจะขับเคลื่อนอินพุต SPI CLK เราจะตรวจสอบส่วนนี้ในภายหลัง เนื่องจากเป็นตรรกะ "หลัก" ที่รับผิดชอบการทำงานที่เหมาะสม รหัสดิจิทัลใหม่จะถูกเก็บไว้ในโมดูล SPI เฉพาะในกรณีที่เป็นของแรงดันไฟฟ้าขาเข้าสูงสุดจริงเท่านั้น

คอมโพเนนต์ DCMP ใช้เพื่อเปรียบเทียบข้อมูล ADC ปัจจุบันกับผู้ชนะคนสุดท้าย (นั่นคือค่าสูงสุดที่พบ) ซึ่งจัดเก็บไว้ในบล็อก SPI มันจะสร้างพัลส์ที่เอาต์พุต OUT+ เมื่อข้อมูล ADC ใหม่มากกว่าข้อมูลก่อนหน้า เราใช้สัญญาณ OUT+ เพื่ออัปเดตบล็อก SPI ด้วยผู้ชนะรายใหม่

สัญญาณนาฬิกาทั่วโลกขับเคลื่อนการแปลง ADC และการกำหนดเวลาทั่วไป เมื่อทำการแปลงแล้ว สัญญาณเอาต์พุต INT ของ ADC จะกะพริบ ประสานกันตามเวลากับเอาต์พุตข้อมูลแบบขนานของ ADC เราใช้เอาต์พุต INT เพื่อเพิ่มตัวนับไบนารี 3 บิตซึ่งใช้งานโดย DFF ใน Matrix1 ซึ่งมีประโยชน์ด้วยเหตุผลสามประการ:

1. สายเอาท์พุตตัวนับจะระบุถึงมัลติเพล็กเซอร์แอนะล็อกภายนอก ดังนั้นจึงให้บริการแรงดันไฟฟ้าอินพุตถัดไปไปยัง ADC

2. การนับจะถูกตรึงไว้ในรีจิสเตอร์ 3 บิต (ใช้ใน Matrix1) เพื่อเก็บผู้ชนะชั่วคราวระหว่างการสแกน

3. การนับจะถูกถอดรหัสเพื่ออัปเดตรีจิสเตอร์ 3 บิตตัวที่สอง (ใช้งานใน Matrix0) เมื่อการสแกนเสร็จสิ้น

ขั้นตอนที่ 3: การใช้งานลอจิก

โมดูล ADC จะจัดเตรียมข้อมูลที่แปลงแล้วของแรงดันไฟฟ้าขาเข้าทั้งหมดตามลำดับโดยไม่มีกำหนด เมื่อ Multiplexer ถูกกำหนดให้เป็น 0b111 (ทศนิยม 7) ตัวนับจะหมุนไปที่ 0b000 (ทศนิยม 0) ดังนั้นจึงเริ่มการสแกนแรงดันไฟฟ้าขาเข้าใหม่

ระหว่างการสแกน สัญญาณเอาท์พุต ADC INT จะถูกสร้างขึ้นเมื่อเอาต์พุตข้อมูลแบบขนานถูกต้อง เมื่อสัญญาณนี้เป็นพัลส์ มัลติเพล็กเซอร์แอนะล็อกต้องสลับไปยังอินพุทถัดไป โดยให้ PGA มีแรงดันไฟฟ้าที่สอดคล้องกัน ดังนั้น เอาต์พุต ADC INT จึงเป็นสัญญาณการตอกบัตรโดยตรงของตัวนับไบนารี 3 บิตของรูปที่ 2 ซึ่งคำเอาต์พุตแบบขนาน 3 บิตจะระบุโดยตรงไปยังมัลติเพล็กเซอร์แอนะล็อกภายนอก (“V เลือก” ในรูปที่ 1)

ให้เราอ้างอิงถึงตัวอย่างที่แรงดันไฟฟ้าขาเข้าควรมีความสัมพันธ์ดังต่อไปนี้:

ก) V0 < V1 < V2

ข) V2 > V3, V4

ค) V5 > V2

รูปที่ 3 แสดงสัญญาณหลักที่เกี่ยวข้องกับกลไกการตัดสินใจสูงสุด

เนื่องจากในที่สุดข้อมูลจะถูกโอเวอร์คล็อกในการลงทะเบียนบัฟเฟอร์ SPI แบบซิงโครนัสกับพัลส์ INT หน้าต่างการเปรียบเทียบจึงมีอยู่โดยที่เนื้อหาบัฟเฟอร์ SPI จะถูกเปรียบเทียบกับผลการแปลง ADC ถัดไป จังหวะเวลาเฉพาะนี้ส่งผลให้เกิดการสร้างพัลส์ OUT+ ที่เอาต์พุต DCMP เราสามารถใช้ประโยชน์จากพัลส์เหล่านี้เพื่อโหลดค่าใหม่ลงใน SPI buffer register

ตามที่เห็นได้จากบรรทัดข้อมูลบัฟเฟอร์ SPI ของรูปก่อนหน้า การลงทะเบียน SPI จะประกอบด้วยค่าที่ยิ่งใหญ่ที่สุดในบรรดาอินพุต 8 รายการทุกครั้ง และจะอัปเดตเมื่อโมดูล DCMP ตรวจพบค่าที่มากกว่าเท่านั้น (หมายถึง DCMP เอาต์พุตบรรทัด OUT+ ของพล็อต พัลส์ที่ขาดหายไปทำให้ V2 ยังคงล็อคอยู่ในรีจิสเตอร์จนกว่าจะเปรียบเทียบกับ V5)

ขั้นตอนที่ 4: การแก้ไขการหยุดชะงัก

หากตรรกะที่นำมาใช้จะเป็นไปตามที่อธิบายไว้ข้างต้น เป็นที่ชัดเจนว่าเราจะชนเข้ากับสถานการณ์การหยุดชะงัก: ระบบสามารถตรวจจับเฉพาะแรงดันไฟฟ้าที่สูงกว่าแรงดันไฟฟ้าที่สอดคล้องกับสิ่งที่เก็บไว้ในบัฟเฟอร์รีจิสเตอร์ SPI

สิ่งนี้ยังใช้ได้ในกรณีที่แรงดันไฟฟ้านี้ลดลงและอินพุตอื่น จนถึงตอนนี้ต่ำกว่านั้นจะกลายเป็นค่าสูงสุด: จะไม่มีการตรวจจับ สถานการณ์นี้อธิบายได้ดีกว่าในรูปที่ 4 ซึ่งมีแรงดันไฟฟ้าอินพุตเพียง 3 ตัวเท่านั้น ความชัดเจน

ในขณะที่ทำซ้ำ 2 V3 จะลดลงและ V1 คือแรงดันไฟฟ้าสูงสุดจริง แต่โมดูล DCMP ไม่ได้ให้พัลส์เนื่องจากข้อมูลที่จัดเก็บในบัฟเฟอร์รีจิสเตอร์ SPI (สอดคล้องกับ 0.6 V) นั้นใหญ่กว่าที่สอดคล้องกับ V1 (0.4 V)

จากนั้นระบบจะทำงานเป็นตัวค้นหาสูงสุด "สัมบูรณ์" และไม่อัปเดตเอาต์พุตอย่างถูกต้อง

วิธีที่ดีในการเอาชนะปัญหานี้คือการบังคับให้โหลดข้อมูลซ้ำใน SPI Buffer Register เมื่อระบบเสร็จสิ้นรอบโพลเต็มของทุกแชนเนล

ในความเป็นจริง หากแรงดันไฟฟ้าที่อินพุตนั้นยังคงสูงที่สุด ไม่มีอะไรเปลี่ยนแปลงและการควบคุมจะทำงานต่อไปอย่างปลอดภัย (อ้างอิงจากรูปที่ 4 ด้านบน นี่เป็นกรณีของ Loop Iterations 0 และ 1) ในทางกลับกัน หากแรงดันไฟฟ้าที่อินพุตนั้นโดยบังเอิญลดลงเป็นค่าที่น้อยกว่าอินพุตอื่น การโหลดค่าใหม่จะทำให้โมดูล DCMP สามารถสร้างพัลส์ OUT+ เมื่อเปรียบเทียบกับค่าสูงสุดใหม่ (นี่คือ กรณีของการวนซ้ำ 2 และ 3)

จำเป็นต้องมีวงจรลอจิกเพื่อเอาชนะปัญหา ต้องสร้างสัญญาณนาฬิกาไปยังส่วนประกอบ SPI เมื่อลูปไปถึงอินพุตสูงสุดจริง ดังนั้นจึงบังคับให้โหลดคำข้อมูลที่อัปเดตลงใน SPI Buffer Register อีกครั้ง ซึ่งจะกล่าวถึงในส่วนที่ 7.2 และ 7.6 ด้านล่าง

ขั้นตอนที่ 5: การกำหนดค่าอุปกรณ์ - Matrix0 Circuit

SLG46620G มีบล็อกเมทริกซ์สองบล็อก ดังแสดงในรูปที่ 2 รูปภาพต่อไปนี้แสดงการกำหนดค่าอุปกรณ์ตามลำดับ

ส่วนบนของวงจรคือ "Loop Register" ที่รับรู้ด้วย 3 DFF (DFF0, DFF1 และ DFF2) จะมีการรีเฟรชหลังจากทุกลูปของอินพุตมัลติเพล็กเซอร์เพื่อส่งไปยังไดรเวอร์การแสดงผล 7 ส่วนเป็นเลขฐานสองของ "ผู้ชนะ" นั่นคืออินพุตที่มีแรงดันไฟฟ้าสูงสุดในการสแกนครั้งล่าสุด ทั้งนาฬิกาสำหรับ DFF และข้อมูลมาจากตรรกะที่ใช้ใน Matrix1 จนถึงพอร์ต P12, P13, P14 และ P15 ตามลำดับ

ส่วนล่างคือส่วนหน้าแบบแอนะล็อกพร้อมอินพุตที่พิน 8 และ PGA พร้อมอัตราขยาย x1 เอาต์พุต ADC INT ไปที่ลอจิกการตอกบัตรของ SPI และไปยัง Matrix1 ผ่านพอร์ต P0 ซึ่งจะทำหน้าที่เป็นสัญญาณนาฬิกาสำหรับตัวนับที่ใช้งาน

เอาต์พุตข้อมูลแบบขนานของ ADC และ SPI มีป้ายกำกับว่า NET11 และ NET15 ตามลำดับ เพื่อเชื่อมต่อกับคอมโพเนนต์ DCMP ใน Matrix1

ขั้นตอนที่ 6: การกำหนดค่าอุปกรณ์ - SPI Clocking Logic

ดังที่ได้กล่าวไว้ก่อนหน้านี้ในส่วน "การนำตรรกะไปใช้" SPI Buffer Register จะได้รับการอัปเดตทุกครั้งที่มีการเปรียบเทียบระหว่างค่าที่จัดเก็บจริงและข้อมูลการแปลง ADC ใหม่สร้างพัลส์ที่เอาต์พุต DCMP OUT+

รับประกันความสมบูรณ์ของสัญญาณหากสัญญาณนี้เป็น AND-ed ด้วยเอาต์พุต ADC INT สิ่งนี้จะหลีกเลี่ยงการขัดขวางและทริกเกอร์ที่ผิดพลาด

เรายังได้เน้นย้ำด้วยว่าหากต้องการข้ามสถานการณ์การชะงักงัน บัฟเฟอร์ SPI จะต้องได้รับการอัปเดตเมื่อลูปเข้าถึงข้อมูลผู้ชนะจริง

สามสัญญาณอยู่ในเกมสำหรับการตอกบัตร SPI ที่เหมาะสม:

1. เอาต์พุต ADC INT (LUT0-IN1)

2. DCMP OUT+ เอาต์พุต (LUT0-IN0 ผ่านพอร์ต P10)

3. นับเท่ากับสัญญาณสลัก (LUT0-IN2 ผ่านพอร์ต P11)

สองอันแรกคือ AND-ed และทั้งคู่ OR-ed กับอันหลังใน LUT0 ซึ่งมีการกำหนดค่าการใช้งานดังในรูปที่ 6

ขั้นตอนที่ 7: การกำหนดค่าอุปกรณ์ - คุณสมบัติคอมโพเนนต์ Matrix0

รูปที่ 7-10 แสดงหน้าต่างคุณสมบัติส่วนประกอบที่เหลือที่เป็นของ Matrix0

ขั้นตอนที่ 8: การกำหนดค่าอุปกรณ์ - วงจร Matrix1

ขั้นตอนที่ 9: การกำหนดค่าอุปกรณ์ - ตัวนับไบนารี 3 บิต

ส่วนบนของวงจรประกอบด้วยองค์ประกอบลอจิก ซึ่งส่วนใหญ่เป็นตัวนับไบนารี 3 บิตที่โอเวอร์คล็อกโดยเอาต์พุต ADC INT ตามที่กล่าวไปแล้ว ตัวนับนี้ใช้กับแผนผัง "มาตรฐาน" ที่แสดงในรูปที่ 12

ตัวนับนี้รับรู้ในการออกแบบของเราโดยใช้ Flip-Flops DFF9, DFF10, DFF11 และ INV1, LUT4, LUT8 เอาต์พุต DFF9 คือ LSB ในขณะที่ DFF11 คือ MSB ดังแสดงในรูปที่ 13

LUT4 ได้รับการกำหนดค่าเป็น XOR ในขณะที่ LUT8 ดำเนินการตรรกะ AND-XOR ของรูปที่ 12

เอาต์พุตตัวนับไปที่พินเอาต์พุตดิจิทัลสามพินเพื่อระบุ Analog Multiplexer ภายนอก

LUT10 ถอดรหัสรหัสของตัวนับเมื่อการสแกนเสร็จสิ้น และป้อนพัลส์ไปยัง Matrix0 ผ่าน DLY8 และพอร์ต P12 สิ่งนี้ทำได้โดยง่ายโดย AND-ing เอาต์พุตของตัวนับ ดังนั้นการถอดรหัสหมายเลข 7 ธ.ค. (0b111 ไบนารี จุดสิ้นสุดของลูป)

ขั้นตอนที่ 10: การกำหนดค่าอุปกรณ์ - ตรรกะเปรียบเทียบ 3 บิต

รูปที่ 15 แสดงวงจรที่ใช้ในการตรวจจับเมื่อมีการวนซ้ำที่ที่อยู่ "ผู้ชนะ" ปัจจุบัน ในกรณีนี้ ดังที่ได้กล่าวไปแล้ว ชีพจรดิจิทัลควรบังคับให้โหลดผลลัพธ์ ADC ปัจจุบันซ้ำเพื่อแก้ไขสถานการณ์การหยุดชะงักที่อาจเกิดขึ้น

ที่อยู่ "ผู้ชนะ" ถูกเก็บไว้ในการลงทะเบียนชั่วคราวของ Matrix1 (ดูด้านล่าง) ในขณะที่ที่อยู่ปัจจุบันจะถูกส่งออกโดยตัวนับไบนารี

ประตู XNOR ให้เอาต์พุตที่แท้จริง (ลอจิก 1 หรือ 'สูง') เมื่ออินพุตทั้งสองเท่ากัน AND-ing สัญญาณนี้สำหรับทุกบิต (LUT9) ทำให้เราชีพจรเมื่อรหัสไบนารีทั้งสองเหมือนกัน รายละเอียดเกี่ยวกับเกท XOR เป็นตัวตรวจสอบพาริตีสามารถพบได้ในเอกสารอ้างอิง

สัญญาณ 'Counter-equals-Latch' จะถูกส่งไปยัง Matrix0 ผ่านพอร์ต P11

ขั้นตอนที่ 11: การกำหนดค่าอุปกรณ์ - ลอจิกเปรียบเทียบดิจิทัลและการลงทะเบียนชั่วคราว

ส่วนล่างของรูปที่ 11 (เน้นในรูปที่ 16) แสดงบล็อก DCMP ซึ่งเป็นส่วนการตัดสินใจของการออกแบบนี้

DFF6, 7 และ 8 สร้างรีจิสเตอร์ 3 บิตเพื่อเก็บหมายเลขอินพุตชั่วคราว "ผู้ชนะ" ในขณะที่ลูปกำลังทำงาน อินพุตของ Flip-Flop คือเอาต์พุตตัวนับไบนารี 3 บิต ซึ่งมองเห็นได้ในวงจร Matrix1 ทั่วโลกของรูปที่ 11 ซึ่งถูกข้ามไปเพื่อความชัดเจน

เอาต์พุตของรีจิสเตอร์นี้ไม่สามารถขับเคลื่อนการแสดงผล 7 ส่วนได้โดยตรง เนื่องจากค่าที่เก็บไว้ที่นี่จะเปลี่ยนแปลงระหว่างการสแกน และควรถือว่า "ใช้ได้" เฉพาะเมื่อสิ้นสุดการสแกนเท่านั้น

ด้วยเหตุนี้ เอาต์พุตรีจิสเตอร์ชั่วคราวจึงเชื่อมต่อกับ Loop Register ของ Matrix0 ผ่านพอร์ตเมทริกซ์ระหว่างเมทริกซ์ P13, P14 และ P15

เป็นสิ่งสำคัญที่ต้องสังเกตในรูปที่ 16 ว่ารีจิสเตอร์ชั่วคราวถูกโอเวอร์คล็อกโดยเอาต์พุต DCMP OUT+ เมื่อ ADC-SPI ลงทะเบียนผลการเปรียบเทียบในค่าสูงสุดใหม่ที่พบ

สัญญาณ OUT+ เดียวกันจะถูกส่งไปยัง Matrix0, SPI CLK Logic ผ่านพอร์ต P10

ขั้นตอนที่ 12: การกำหนดค่าอุปกรณ์ - คุณสมบัติคอมโพเนนต์ Matrix1

รูปที่ 17-19 แสดงหน้าต่างคุณสมบัติส่วนประกอบที่เป็นของ Matrix1

ขั้นตอนที่ 13: ผลลัพธ์

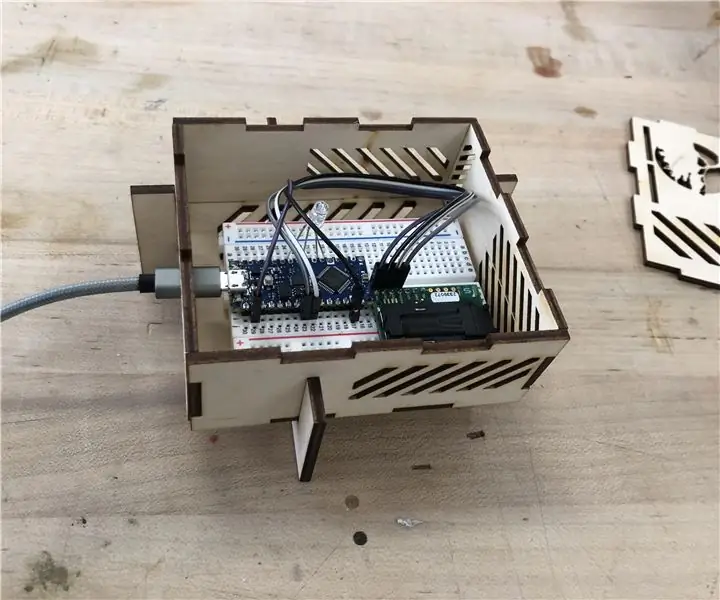

ในการทดสอบการใช้งาน ได้มีการสร้างต้นแบบของบอร์ดประเมินผล โดยที่แรงดันไฟฟ้าอินพุตแบบอนาล็อก 8 ตัวได้มาจากชุดตัวแบ่งตัวต้านทานที่มี TrimPots (ดังแสดงในรูปที่ 20)

มัลติเพล็กเซอร์ที่ใช้คือ ADG508 ซึ่งเป็นชิ้นส่วนที่สามารถทำงานได้โดยใช้การจ่ายไฟเพียงครั้งเดียว (12 V)

ไดรเวอร์การแสดงผล 7 ส่วนคือ 74LS47 มันถอดรหัสคำอินพุตแบบขนานและขับจอแสดงผล 7 เซ็กเมนต์ขั้วบวกทั่วไปโดยตรง

บอร์ดประเมินผลมีคอนเน็กเตอร์มุมขวา 2x10 เพื่อเสียบเข้ากับ GreenPAK Advanced Development Platform โดยตรงที่คอนเน็กเตอร์ส่วนขยายดังแสดงในรูปที่ 21

การทำงานร่วมกับ GreenPAK Advanced Development Platform ทำให้ง่ายต่อการวัดสัญญาณเพื่อตรวจสอบอย่างรวดเร็ว ตัวอย่างเช่น รูปที่ 22 แสดงชุดสัญญาณ (ตามลำดับ CLOCK, เอาต์พุต ADC INT และเอาต์พุต DCMP OUT+) ตามที่จับโดย HP 54620A Logic Analyzer รูปคลื่นถูกกระตุ้นโดยขอบที่เพิ่มขึ้นของสัญญาณ OUT+ (บนขอบเขตที่มีป้ายกำกับว่า 'A>B') ดังนั้นนี่คือการจับรูปคลื่นเมื่อตรวจพบแรงดันไฟฟ้าสูงสุดใหม่ระหว่างอินพุตแบบอะนาล็อก อันที่จริง ได้มาจากการหมุน TrimPots ตัวใดตัวหนึ่งของคณะกรรมการประเมินผลเพื่อเพิ่มแรงดันไฟที่แสดงในรูปที่ 22

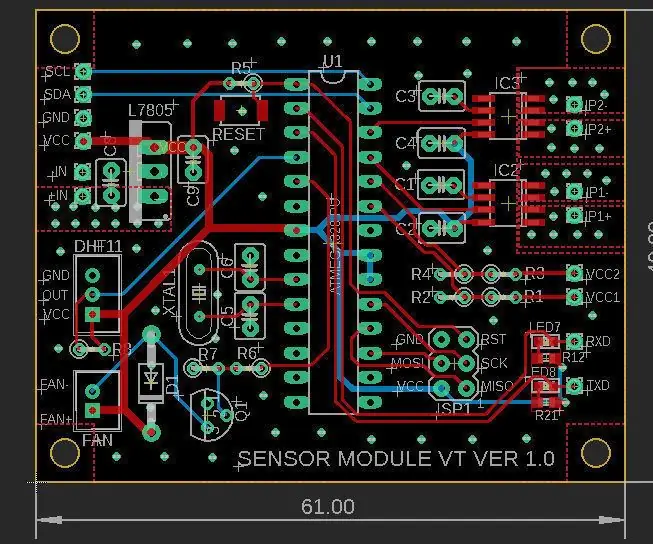

รูปที่ 23 แสดงแผนผังของคณะกรรมการประเมินผล

บทสรุป

ในคำแนะนำนี้ เราใช้ตัวค้นหาแรงดันไฟฟ้าสูงสุด (หรือต่ำสุด) แปดช่องสัญญาณเพื่อใช้เป็นส่วนเสริมทั่วไปในระบบควบคุมหลายช่องสัญญาณ วิธีการที่นำเสนอนี้ใช้ประโยชน์จากคุณลักษณะขั้นสูงของส่วนประกอบ GreenPAK และแสดงให้เห็นว่าเป็นไปได้อย่างไรที่จะผสานรวมในฟังก์ชันอนาล็อกและดิจิตอลชิปตัวเดียว IC เชิงพาณิชย์หลายตัวสามารถแทนที่ด้วย Dialog GreenPAK เพื่อลดขนาดและต้นทุนของแอปพลิเคชัน

แนะนำ:

PORTABLE MINI MULTI VOLTAGE PSU พร้อม USB, ไฟฉาย, เครื่องทดสอบส่วนประกอบและเครื่องชาร์จในตัว: 6 ขั้นตอน

PORTABLE MINI MULTI VOLTAGE PSU พร้อม USB, ไฟฉาย, เครื่องทดสอบส่วนประกอบและเครื่องชาร์จในตัว: ยินดีต้อนรับสู่คำสั่งแรกของฉัน! ด้วยคำแนะนำนี้คุณสามารถเปลี่ยนธนาคารพลังงานแสงอาทิตย์ที่หลบภัย / ราคาถูก (พร้อมชิ้นส่วนพิเศษบางส่วน) เป็นสิ่งที่มีประโยชน์ สิ่งที่คุณสามารถใช้ทุกวันเช่นฉัน เพราะมันยอดเยี่ยมมากที่จะใช้! ส่วนใหญ่ AV

Max MSP Ambient Loop Generator: 19 ขั้นตอน

Max MSP Ambient Loop Generator: นี่คือบทช่วยสอนเกี่ยวกับวิธีเริ่มต้นสร้างตัวสร้างแอมเบียนต์ลูปใน Max MSP บทช่วยสอนนี้คาดหวังให้คุณมีความเข้าใจพื้นฐานเกี่ยวกับ Max MSP, อินเทอร์เฟซ DAW และการประมวลผลสัญญาณ หากคุณต้องการใช้โปรแกรมที่ออกแบบในบทช่วยสอนนี้

Arduino Dual Channel Voltage Sensor Module: 8 ขั้นตอน

โมดูลเซ็นเซอร์แรงดันไฟฟ้าสองช่องของ Arduino: สองสามปีแล้วที่ฉันเขียนคำสั่งได้ ฉันคิดว่าถึงเวลาที่จะกลับมาแล้ว ฉันต้องการสร้างเซ็นเซอร์วัดแรงดันไฟฟ้าเพื่อให้สามารถเชื่อมต่อกับแหล่งจ่ายไฟแบบตั้งโต๊ะได้ ฉันมีพาวเวอร์ซัพพลายแบบแปรผันสองแชนเนล มันมีเ

La Chaise Longue Interactive Avec Arduino Et Max/MSP.: 5 ขั้นตอน

La Chaise Longue Interactive Avec Arduino Et Max/MSP.: L'idée est de créer une chaise longue interactive: un utilisateur qui s'assoit dans le transat déclenche une climate sonore et visuelle lui rappelant la mer, la plage… การใช้งานที่หลากหลาย donc un capteur de luminosité (สถานที่ ซู เลอ ทรานแซท) reliés à

Spline Modeling Flower Blossoms ใน 3DS MAX สำหรับการพิมพ์ 3 มิติ: 7 ขั้นตอน (พร้อมรูปภาพ)

Spline Modeling Flower Blossoms ใน 3DS MAX สำหรับการพิมพ์ 3D: ในคำแนะนำนี้ คุณจะได้เรียนรู้เคล็ดลับเกี่ยวกับวิธีสร้างดอกไม้ที่ดูเป็นธรรมชาติใน 3DS Max สำหรับการพิมพ์ 3 มิติสำหรับของขวัญที่ไม่ซ้ำใครสำหรับวันหยุด เช่น วันแม่หรือวันวาเลนไทน์ ข้อกำหนด: การทดลองใช้งาน หรือสำเนาส่วนตัวของ Autodesk 3ds Max เกร็ดน่ารู้