สารบัญ:

- ผู้เขียน John Day day@howwhatproduce.com.

- Public 2024-01-30 13:03.

- แก้ไขล่าสุด 2025-01-23 15:12.

JDM เป็นโปรแกรมเมอร์ PIC ที่ได้รับความนิยม เนื่องจากใช้พอร์ตอนุกรม ส่วนประกอบขั้นต่ำสุดเปลือย และไม่ต้องใช้แหล่งจ่ายไฟ แต่มีความสับสนเกิดขึ้นกับโปรแกรมเมอร์หลายรูปแบบบนเน็ต อันไหนใช้งานได้กับ PIC ตัวไหน ? ใน "คำแนะนำ" นี้ เราได้นำ JDM ไปทดสอบ และผมสาธิตวิธีจำลองวงจรโดยใช้ Spice ซึ่งจะตอบคำถามของคุณทั้งหมด!

เสบียง

LTspice ซึ่งสามารถดาวน์โหลดได้จาก Analog Devices ที่นี่

คุณต้องใช้ไฟล์วงจร JDM ที่นี่

ขั้นตอนที่ 1: ข้อกำหนดพอร์ตอนุกรม

JDM ต้องการพอร์ตอนุกรมที่ตรงตามข้อกำหนด EIA232 ซึ่งเหมาะกับระดับแรงดันไฟฟ้า +12/-12

ตามแผ่นข้อมูล Texas Instruments Line Driver MC1488 (รูปที่ 3)

อิมพีแดนซ์เอาต์พุต = 4V/8mA = 500 โอห์ม

ขีด จำกัด กระแสลัดวงจร = 12mV โดยไม่มีการ จำกัด เวลา - ไม่ทำลายชิป

อิมพีแดนซ์อินพุตของเครื่องรับสาย = 3k ถึง 7k ohm ที่แนะนำ

พอร์ตอนุกรมบนเดสก์ท็อปพีซีรุ่นเก่าใช้ +12v/-12V ที่ตรงตามข้อกำหนดนี้

พอร์ตอนุกรมบนแล็ปท็อปพีซีรุ่นใหม่ใช้แรงดันไฟฟ้าที่ต่ำกว่า JDM อาจใช้หรือไม่ได้ผล - คำตอบนั้นซับซ้อนกว่า

ขั้นตอนที่ 2: ข้อกำหนดการเขียนโปรแกรม PIC

ข้อมูลเกี่ยวกับข้อกำหนดในการเขียนโปรแกรม PIC ได้มาจาก Microchip ข้างต้นสำหรับอุปกรณ์ทั่วไป

ขั้นตอนที่ 3: ข้อกำหนด JDM

เว็บไซต์ JDM ดั้งเดิมได้สูญหายไปในห้วงเวลาหรือไม่? สิ่งนี้ทำให้เราเดาได้ว่าผู้ออกแบบเดิมตั้งใจไว้สำหรับข้อกำหนดนี้อย่างไร

- ระบุ VDD=5V และสูงสุด IDD=2mA (สำหรับเวอร์ชัน "ในซ็อกเก็ต")

- ให้ VHH=13V และสูงถึง IHH=0.2mA สูงสุด

- MCLR เวลาเพิ่มขึ้น tVHHR = สูงสุด 1uS

- เวอร์ชัน ICSP ต้องสามารถดึง MCLR ให้ต่ำเมื่อเทียบกับการดึงเป้าหมาย 22k

ขั้นตอนที่ 4: คำอธิบายวงจร

รูปที่ JDM1 ขึ้นอยู่กับวงจร JDM "มาตรฐาน" ที่นำมาจากเว็บไซต์ PICPgm นี่คือโปรแกรมเมอร์ "PIC in Socket" ที่ PIC ใช้พลังงานจากพิน TX และ RTS ไดอะแกรมดั้งเดิมนั้นเข้าใจยาก ดังนั้นฉันจึงวาดใหม่โดยใช้แบบแผนปกติของการไหลของกระแสจากบนลงล่าง และฉันได้เพิ่มไฟ LED "RESET", "PROG" และ "RTS" ซึ่งจำเป็นในระหว่างการก่อสร้างและการทดสอบ หวังว่าสิ่งเหล่านี้จะไม่ส่งผลเสียต่อพฤติกรรม

แบบแผนปกติของการออกแบบวงจรคือการต่อกราวด์ทั้งหมด แต่คุณสมบัติหลักของ JDM คือกราวด์พอร์ตอนุกรม (GND) เชื่อมต่อกับ VDD สิ่งนี้สร้างความสับสนเนื่องจากสัญญาณพอร์ตอนุกรมถูกวัดด้วยความเคารพต่อสัญญาณ GND, PIC ที่เกี่ยวกับลอจิกกราวด์ (VSS)

เมื่อ TX สูงขึ้น Q1 จะทำงานเป็นไดโอดลำเอียงไปข้างหน้าสองตัว (ตัวสะสม Q1 ไม่เอนเอียงแบบย้อนกลับเหมือนกับการทำงานของทรานซิสเตอร์ปกติ) ตัวรวบรวม Q1 ชาร์จ C2 ซึ่งถูกยึดที่ VDD+8V โดย Zener (D3) อีซีแอล Q1 ส่ง 13V ไปยัง MCLR สำหรับโหมดโปรแกรม/ตรวจสอบ

เมื่อ TX ต่ำ ตัวเก็บประจุ C3 จะถูกชาร์จผ่าน D1 และ VSS จะถูกจับที่ VDD-5V โดยซีเนอร์ (D5) นอกจากนี้ TX ยังยึดที่ (VSS-0.6) โดย D1 Q1 ปิดอยู่ C1 จะเก็บค่าใช้จ่ายสำหรับพัลส์การเขียนโปรแกรมครั้งต่อไป MCLR ถูกยึดที่ 0V โดย D2 ดังนั้น PIC จะถูกรีเซ็ต

เมื่อ RTS สูง นาฬิกาจะถูกส่งไปยัง PGC D4 แคลมป์ PGC ที่ตรรกะ VDD สูง เมื่อ RTS ต่ำ ตัวเก็บประจุ C3 จะถูกชาร์จผ่าน D6 และ VSS จะถูกจับที่ VDD-5V โดยซีเนอร์ (D5) D6 แคลมป์ PGC ที่ VSS หรือลอจิก 0

ในระหว่างการตั้งโปรแกรม ข้อมูลที่ส่งออกบน DTR จะถูกอ่านบน PGD ซึ่ง PIC กำหนดค่าเป็นอินพุต เมื่อ DTR สูง Q2 จะทำหน้าที่เป็น “ผู้ติดตามอีซีแอล” และแรงดัน PGD อยู่ที่ประมาณ (VDD-0.6) หรือตรรกะ 1 เมื่อ DTR ต่ำ Q2 จะทำหน้าที่เป็นทรานซิสเตอร์ที่ไม่ดี (พินตัวปล่อยและตัวสะสมกลับด้าน) Q2 ดึง PGD ให้ต่ำ ซึ่ง D7 ยึดไว้ที่ VSS หรือตรรกะ 0

ระหว่างการตรวจสอบ PIC จะกำหนดค่า PGD เป็นเอาต์พุตสำหรับการส่งข้อมูลไปยังพอร์ตอนุกรม ต้องตั้งค่า DTR ให้สูงและอ่านข้อมูลบน CTS เมื่อเอาต์พุต PGD สูง Q2 จะปิด CTS = DTR = +12V เมื่อเอาต์พุต PGD ต่ำ Q2 จะเปิดขึ้น ตัวรวบรวม Q2 ดึงกระแส (12V+5V)/(1k+1k5)=7mA จาก DTR และดึง CTS ต่ำไปยัง VSS

ขั้นตอนที่ 5: เตรียมพร้อมสำหรับการจำลอง

ดาวน์โหลด LT spice บันทึกและเปิดไฟล์วงจร (*.asc) ที่ให้ไว้ที่นี่ ในการจำลองวงจร เราต้องป้อนอินพุตบางส่วน จากนั้นจึง "ติดตาม" เอาต์พุต V1, V2 V3 จำลองพอร์ตอนุกรม 12V พร้อมอิมพีแดนซ์เอาต์พุต R11, R12, R13

- V1 สร้าง 2 Program Pulses บน TX จาก 0.5ms ถึง 4.5ms

- V2 สร้างพัลส์ข้อมูลจำนวนมากบน DTR จาก 1.5 เป็น 4.5ms

- V3 สร้างพัลส์นาฬิกาเป็นชุดบน RTS จาก 0.5 เป็น 3.5ms

ส่วนประกอบ V4, X1, R15 และ R16 ล้วนเป็นส่วนหนึ่งของการจำลอง

- V4 สร้าง 2 พัลส์จาก 2.5 ถึง 4.5ms สำหรับตรวจสอบข้อมูล

- Jumper X1 จำลอง OUTPUT บน PGD

- R15, R16 จำลอง "กำลังโหลด" ของ PIC บน VDD และ MCLR

ขั้นตอนที่ 6: การปรับเปลี่ยนสำหรับ ICSP

รูปที่ JDM3 แสดงเวอร์ชันสำหรับการเขียนโปรแกรม "ในวงจร" ดัดแปลงจากเดิมคือ

- เปลี่ยนซ็อกเก็ต ZIF ด้วยขั้วต่อ ICSP

- PIC ได้รับพลังงานจากวงจรจ่ายไฟไปยังวงจรเป้าหมาย (V5)

- ลบซีเนอร์ 5V (D5)

- ตัวเก็บประจุขนาดเล็ก 100pF (C4) ถูกย้ายถัดจาก PIC บนวงจรเป้าหมาย

- ไฟ LED จะใช้พลังงานจากแผงวงจรหากเป็นไปได้

- ต้องใช้ตัวต้านทานแบบดึงขึ้น MCLR (R10) และไดโอด (D10) ในวงจรเป้าหมาย

- คำเตือน. กระดานเป้าหมายต้องมีแหล่งจ่ายแบบ "ลอยตัว" ซึ่งควรเป็นแบตเตอรี่

- ห้ามเชื่อมต่อกราวด์เป้าหมาย (VSS) กับกราวด์คอมพิวเตอร์/พีซีโดยเชื่อมต่อพอร์ตคอมพิวเตอร์อื่นๆ พร้อมกันกับ JDM

หลังจากจำลอง JDM1 ปัญหาของเวลาในการชาร์จนานใน C2 ก็ชัดเจนขึ้น จากนั้นหลังจากอ่าน Fruttenboel ปรากฏว่า C2 และ Q1 ถูกเพิ่มเข้ามาเป็นการดัดแปลงจากต้นฉบับ ฉันไม่สามารถคิดได้ว่า C2 และ Q1 ตั้งใจจะทำอะไรนอกจากสร้างปัญหา ดังนั้นสำหรับ JDM4 เราจึงเปลี่ยนกลับเป็นการออกแบบที่เก่ากว่าบน Fruttenboel ซึ่งเข้าใจง่ายและตรงไปตรงมา D1 และ D3/LED2 แคลมป์ MCLR ระหว่าง VSS และ VDD+8V ค่าของ R1 ลดลงเหลือ 3k3 เพียงเพียงพอที่จะให้ LED2 สว่างที่ 12V

JDM4 ยังได้รับการออกแบบเพื่อทำงานกับพอร์ตอนุกรมที่อ่อนแอกว่า เมื่อ TX สูง (+9V) แหล่งจ่ายกระแส TX = (9-8)/(1k +3k3) = 0.2ma เพียงพอที่จะดึง MCLR ให้สูง แม้ว่าจะไม่เพียงพอที่จะส่องสว่าง LED2 เมื่อ TX ต่ำ (ประมาณ -7V) กระแส TX ซิงก์ =(9-7)/1k = 2mA กระแสไฟ LED1 = (7-2 สำหรับไฟ LED)/(2k7) = 1.8mA MCLR ดึงกระแส = 7-5.5/3k3 = 0.5mA

วงจรนี้ยังได้รับการทดสอบ (การจำลอง JDM5) เพื่อดูว่าเกิดอะไรขึ้นกับพอร์ตอนุกรมขั้นต่ำ +/-7V ซึ่งแรงดันไฟฟ้าไม่เพียงพอที่จะคง VHH=13V จุดประสงค์ของ C1 ตอนนี้ชัดเจน C1 สร้าง +ve boost สั้น ๆ ให้กับ MCLR ซึ่งเพิ่มขึ้น 33us บนขอบที่เพิ่มขึ้นของ TX นานเพียงพอสำหรับ PIC เพื่อเข้าสู่โหมดการเขียนโปรแกรมบางที ? แต่ให้ถอดจัมเปอร์ X2 (ปิดใช้งาน LED1) เนื่องจากมีกระแสไฟไม่เพียงพอที่จะดึง MCLR ให้ต่ำและให้ LED1 สว่างขึ้นพร้อมกัน เมื่อ TX ต่ำ กระแส TX ซิงก์ = (7V-5.5V)/(1k+3k3) = 0.3mA เพียงพอที่จะดึง MCLR ให้ต่ำเมื่อเทียบกับ R10 แบบดึงขึ้น

ขั้นตอนที่ 7: ผลการจำลอง

หากต้องการดูไฟล์กราฟิก ให้คลิกขวาที่ลิงก์ด้านล่าง จากนั้นเลือก "เปิดลิงก์ในแท็บใหม่"

การจำลอง 1: ติดตาม MCLR, VSS และ RTS สำหรับ JDM1 ดั้งเดิม การสังเกต 1, 2 และ 3 จะปรากฏทันที

การจำลอง 2: การติดตาม MCLR และ VSS และ RTS สำหรับ JDM2 ที่แก้ไข ซึ่งแก้ไขปัญหาก่อนหน้านี้

การจำลอง 3: ติดตาม PGD, VSS และ PGC สำหรับ JDM2 ที่ส่งข้อมูลในโหมดโปรแกรม การสังเกต 4 ที่ 3.5mS

การจำลอง 4: ติดตาม PGD, VSS และ CTS สำหรับ JDM2 ในโหมดตรวจสอบ (ใส่จัมเปอร์ X1) ตกลง

การจำลอง 5: ติดตาม MCLR, VSS, PGD และ PGC สำหรับ JDM3 ICSP ใช้พลังงานจากวงจรแก้ปัญหาได้มากมาย

การจำลอง 6: การติดตาม MCLR, VSS, PGD และ PGC สำหรับ JDM4 พร้อมพอร์ตอนุกรม +/-9V MCLR เพิ่มขึ้นทันที ทำงานเต็มที่

การจำลอง 7: การติดตาม MCLR, VSS และ TX สำหรับ JDM5 โดยถอดพอร์ตอนุกรม +/-7V และจัมเปอร์ X2 ออก C1 สร้าง +ve boost (สไปค์) บนขอบที่เพิ่มขึ้นของ MCLR ซึ่งเพียงพอที่จะดัน MCLR เหนือ TX เป็น 13V

ขั้นตอนที่ 8: บทสรุป

เครื่องเทศสามารถเปิดเผย "ความลับที่ซ่อนอยู่" ของการทำงานของวงจรได้ดีมาก เห็นได้ชัดว่าวงจร JDM ทำงานได้และเข้ากันได้กับชิป PIC หลายตัว แต่ข้อสังเกตต่อไปนี้เผยให้เห็นข้อจำกัดที่เป็นไปได้/ปัญหาความเข้ากันได้/ข้อผิดพลาด ?

- เวลาเพิ่มขึ้นนานของ MCLR ในขณะที่ C2 ชาร์จไปยัง VPP ในพัลส์แรกของ TX ล้มเหลวในข้อกำหนด 3

- พอร์ตอนุกรมจะชาร์จ C2 เมื่อ TX สูงและ RTS ต่ำ แต่ RTS ก็มีหน้าที่ชาร์จ C3 เช่นกัน เมื่อทั้งสองเกิดขึ้นพร้อมกัน จะทำให้เกิดภาระมากขึ้นใน RTS ดังนั้น C3 จะสูญเสียประจุ (VSS เพิ่มขึ้น) ที่ 2 มิลลิวินาทีในการจำลอง ล้มเหลวในข้อกำหนด 1

- C3 สูญเสียประจุ (VSS เริ่มสูงขึ้น) หลังจากที่สัญญาณนาฬิกาหยุดที่ 3.5ms

- วัตถุประสงค์ของ C2 คืออะไร จำเป็นเลย ?

โซลูชั่น

- สันนิษฐานว่า PICPgm ใช้ซอฟต์แวร์ "รอบการทำงาน" ต้องใช้พัลส์ TX แบบยาวเพื่อชาร์จล่วงหน้าไปที่ C2 จากนั้นเข้าสู่โหมดการเขียนโปรแกรมหลังจากพัลส์ TX ที่สองเท่านั้น สำหรับการจำลอง ฉันลดค่า C2 เป็น 1uF เพื่อให้เวลาเพิ่มขึ้น 1ms ไม่ใช่ทางออกที่ดี

- แยก C2 และ C3 เพื่อให้ชาร์จแยกกัน การดัดแปลงเล็กน้อยใน JDM2, C2 อ้างอิงถึง GND แทน VSS

- แก้ไขโดย JDM3 ICSP มีความน่าเชื่อถือมากกว่ามาก เนื่องจาก PIC ขับเคลื่อนโดยวงจรเป้าหมาย

- JDM4 แก้ปัญหาที่ 1 นี่คือการออกแบบที่ตรงไปตรงมาเพื่อกำจัด C2 ทั้งหมด

ขั้นตอนที่ 9: และสุดท้าย

หลักฐานของพุดดิ้งอยู่ในการกิน JDM นี้ใช้งานได้ดีจึงใช้ต่อไป

และคำแนะนำของฉันคือ:

- ใช้ JDM2 สำหรับการเขียนโปรแกรมซ็อกเก็ตและพอร์ตอนุกรม 12V

- ใช้ JDM4 สำหรับโปรแกรมเมอร์ ICSP และพอร์ตอนุกรมที่สูงกว่า +/-9V

- ใช้ JDM4 โดยถอดจัมเปอร์ X2 สำหรับพอร์ตอนุกรมที่สูงกว่า +/-7V

ข้อมูลอ้างอิง:

Analog Devices LT เครื่องเทศ

picpgm

ฟรุตเตนโบเอล

ติดตามโครงการ PIC เพิ่มเติมได้ที่ sly-corner

แนะนำ:

การออกแบบเกมในการสะบัดใน 5 ขั้นตอน: 5 ขั้นตอน

การออกแบบเกมในการสะบัดใน 5 ขั้นตอน: การตวัดเป็นวิธีง่ายๆ ในการสร้างเกม โดยเฉพาะอย่างยิ่งเกมปริศนา นิยายภาพ หรือเกมผจญภัย

การตรวจจับใบหน้าบน Raspberry Pi 4B ใน 3 ขั้นตอน: 3 ขั้นตอน

การตรวจจับใบหน้าบน Raspberry Pi 4B ใน 3 ขั้นตอน: ในคำแนะนำนี้ เราจะทำการตรวจจับใบหน้าบน Raspberry Pi 4 ด้วย Shunya O/S โดยใช้ Shunyaface Library Shunyaface เป็นห้องสมุดจดจำใบหน้า/ตรวจจับใบหน้า โปรเจ็กต์นี้มีจุดมุ่งหมายเพื่อให้เกิดความเร็วในการตรวจจับและจดจำได้เร็วที่สุดด้วย

วิธีการติดตั้งปลั๊กอินใน WordPress ใน 3 ขั้นตอน: 3 ขั้นตอน

วิธีการติดตั้งปลั๊กอินใน WordPress ใน 3 ขั้นตอน: ในบทช่วยสอนนี้ ฉันจะแสดงขั้นตอนสำคัญในการติดตั้งปลั๊กอิน WordPress ให้กับเว็บไซต์ของคุณ โดยทั่วไป คุณสามารถติดตั้งปลั๊กอินได้สองวิธี วิธีแรกคือผ่าน ftp หรือผ่าน cpanel แต่ฉันจะไม่แสดงมันเพราะมันสอดคล้องกับ

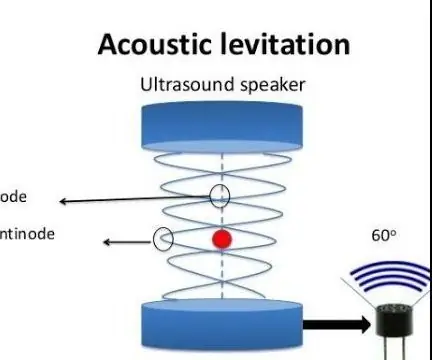

การลอยแบบอะคูสติกด้วย Arduino Uno ทีละขั้นตอน (8 ขั้นตอน): 8 ขั้นตอน

การลอยแบบอะคูสติกด้วย Arduino Uno ทีละขั้นตอน (8 ขั้นตอน): ตัวแปลงสัญญาณเสียงล้ำเสียง L298N Dc ตัวเมียอะแดปเตอร์จ่ายไฟพร้อมขา DC ตัวผู้ Arduino UNOBreadboardวิธีการทำงาน: ก่อนอื่น คุณอัปโหลดรหัสไปยัง Arduino Uno (เป็นไมโครคอนโทรลเลอร์ที่ติดตั้งดิจิตอล และพอร์ตแอนะล็อกเพื่อแปลงรหัส (C++)

เครื่อง Rube Goldberg 11 ขั้นตอน: 8 ขั้นตอน

เครื่อง 11 Step Rube Goldberg: โครงการนี้เป็นเครื่อง 11 Step Rube Goldberg ซึ่งออกแบบมาเพื่อสร้างงานง่ายๆ ในรูปแบบที่ซับซ้อน งานของโครงการนี้คือการจับสบู่ก้อนหนึ่ง