สารบัญ:

- ผู้เขียน John Day day@howwhatproduce.com.

- Public 2024-01-30 13:07.

- แก้ไขล่าสุด 2025-01-23 15:12.

นี่คือบทช่วยสอนเกี่ยวกับวิธีสร้างนาฬิกาจับเวลาหนึ่งนาทีโดยใช้ VHDL และบอร์ด Basys 3 อุปกรณ์ดังกล่าวเหมาะอย่างยิ่งสำหรับเกมที่ผู้เล่นแต่ละคนมีเวลาสูงสุดหนึ่งนาทีในการเคลื่อนไหว นาฬิกาจับเวลาจะแสดงวินาทีและมิลลิวินาทีบนจอแสดงผลเจ็ดส่วนได้อย่างแม่นยำ โดยเริ่มต้นที่ 0 วินาทีและ 0 มิลลิวินาที สูงสุด 60 วินาทีและ 0 มิลลิวินาที นอกจากนี้ยังใช้ปุ่มสองปุ่ม ได้แก่ ปุ่มกลาง ใช้เพื่อเริ่ม หยุด และดำเนินการจับเวลาต่อ และปุ่มขวาใช้เพื่อเริ่มจับเวลาใหม่ เมื่อเปรียบเทียบอุปกรณ์แบบเคียงข้างกันกับนาฬิกาจับเวลาในตัวของสมาร์ทโฟน ความแม่นยำของนาฬิกาจะสังเกตเห็นได้ชัดเจน

ขั้นตอนที่ 1: รับฮาร์ดแวร์/ซอฟต์แวร์

1. Basys 3 Artix-7 FPGA Trainer Board จาก Digilent พร้อมสาย Micro-USB เป็น USB

2. Vivado 2016.2 Design Suite จาก Xilinx

ขั้นตอนที่ 2: บล็อกไดอะแกรม

วงจรนี้สร้างขึ้นตามพฤติกรรมและใช้ส่วนประกอบ Xilinx ในตัว แต่ยังสามารถอธิบายเชิงโครงสร้างได้ดังที่แสดงโดยแผนภาพโครงสร้างทั่วไปด้านบน จากแผนภาพจะเห็นได้ว่าวงจรขับเคลื่อนด้วยตัวแบ่งความถี่สองตัว ตัวแบ่งความถี่ตัวใดตัวหนึ่งทำงานที่ 1 เซนติเมตรและขับตัวนับแคโทดที่ใช้เป็นตัวเลขที่แสดงบนจอแสดงผลเจ็ดส่วน ตัวแบ่งความถี่ที่สองทำงานที่ 240Hz และใช้เพื่อขับเคลื่อนตัวนับแอโนดที่หมุนผ่านแอโนดเพื่อให้ตัวเลขทั้งหมดแสดงอย่างถูกต้องบนจอแสดงผลเจ็ดส่วน ตัวเข้ารหัสใช้ตรรกะแคโทดจากตัวนับแคโทดและตรรกะแอโนดจากตัวนับแอโนด และเข้ารหัสไปยังแคโทดและแอโนดของเอาต์พุตที่เรียกใช้การแสดงผลเจ็ดส่วน หน้าที่ของตัวเข้ารหัสนี้มีไว้สำหรับเอาต์พุตแคโทดเพื่อเปลี่ยนทุกครั้งที่เอาต์พุตแอโนดเปลี่ยนแปลง ไม่สามารถรันเอาต์พุตแคโทดแยกจากตัวนับได้ เนื่องจากแอโนดต้องหมุนผ่านตัวเลข 4 หลักแยกกัน

ขั้นตอนที่ 3: โมดูลโครงการ

ประการแรก บล็อกกระบวนการสำหรับ CEN ถูกสร้างขึ้นเพื่อที่ว่าเมื่อตรวจพบการกดปุ่ม ENABLE จะสลับไปมา ทำหน้าที่เป็นจุดหยุด/เริ่มต้นของตัวนับแคโทด

ในบล็อกกระบวนการถัดไป สัญญาณนาฬิกาในหน่วยเซนติเมตรและ 240Hz จะถูกตั้งค่าเพื่อให้ตัวนับเพิ่มขึ้น 1 ทุกครั้งที่นาฬิกาภายใน 100mHz ถึงขอบที่เพิ่มขึ้น เมื่อตัวนับเซนติเมตรถึง 500,000 มันจะรีเซ็ตกลับเป็น 0 ในขณะเดียวกันตัวนับ 240Hz จะรีเซ็ตเมื่อจำนวนถึง 41667

สำหรับส่วนแคโทดของโค้ด ถ้า ENABLE เป็น '0' การนับแคโทดจะหยุดชั่วคราว หากกดปุ่มรีเซ็ตในช่วงเวลานี้ การนับทั้งหมดจะรีเซ็ตเป็น "0000" ในขณะเดียวกัน หาก ENABLE เป็น '1' การนับแคโทดจะดำเนินต่อไปจนกว่าจำนวนแคโทดจะถึง 60.00 ซึ่งจะทริกเกอร์สัญญาณหยุดเป็น '1' สัญญาณหยุดจะกลับไปที่บล็อกกระบวนการ CEN และทำให้ ENABLE เป็น '0' ในขณะที่สัญญาณหยุดเป็น '1' และจะไม่เปลี่ยนแปลงจนกว่าจะกดปุ่มรีเซ็ต

สุดท้าย การแสดงเจ็ดเซ็กเมนต์ได้รับการตั้งค่าโดยให้ 4 แอโนดเชื่อมต่ออย่างถูกต้องกับแคโทดทั้ง 8 อัน เพื่อแสดงตัวเลข 0-9 ตามลำดับพร้อมกัน

ขั้นตอนที่ 4: ข้อจำกัด

ไฟล์ข้อจำกัดนี้เชื่อมต่ออินพุตและเอาต์พุตที่ระบุจาก VHDL เข้ากับส่วนทางกายภาพที่จำเป็นของบอร์ด Basy สำหรับโปรเจ็กต์นี้ ส่วนประกอบต่างๆ จะประกอบด้วยแอโนดสี่ตัวและแคโทดทั้งแปดตัวสำหรับการแสดงผลเจ็ดส่วน นาฬิกาภายใน 100 mHz ปุ่มกลาง และปุ่มขวา

ขั้นตอนที่ 5: ทดสอบ

เมื่อคุณทำโค้ดเสร็จแล้ว คุณสามารถตั้งโปรแกรม FPGA ผ่านสาย USB ได้ การแสดงเจ็ดส่วนควรแสดง 0.00 ทดสอบเพื่อดูว่าปุ่มทำงานหรือไม่โดยกดปุ่มกลางเพื่อเริ่มจับเวลาจนถึง 60.00 และหยุด คุณสามารถกดปุ่มกลางอีกครั้งเพื่อหยุดชั่วคราวได้ตลอดเวลา เมื่อหยุดชั่วคราว คุณสามารถกดปุ่มขวาเพื่อรีเซ็ตตัวจับเวลากลับเป็น 0.00 หากทุกอย่างถูกต้อง ขอแสดงความยินดีที่คุณได้สร้างตัวจับเวลาหนึ่งนาที!

แนะนำ:

Cordic Algorithm ใช้ VHDL: 4 ขั้นตอน

Cordic Algorithm โดยใช้ VHDL: ## เป็นลิงก์ที่ได้รับความนิยมสูงสุดใน Google สำหรับการนำ VHDL ไปใช้ของ CORDIC ALGORITHM เพื่อสร้างคลื่นไซน์และโคไซน์## ในปัจจุบัน มีอัลกอริธึมที่มีประสิทธิภาพด้านฮาร์ดแวร์จำนวนมาก แต่ก็ยังไม่เป็นที่ทราบกันดีเนื่องจาก การครอบงำของซอฟต์แวร์

การออกแบบตัวควบคุมแคชเชื่อมโยงชุดสี่ทางอย่างง่ายใน VHDL: 4 ขั้นตอน

การออกแบบ Simple Four-way Set Associative Cache Controller ใน VHDL: ในคำสั่งก่อนหน้าของฉัน เราเห็นวิธีการออกแบบตัวควบคุมแคชที่แมปโดยตรงอย่างง่าย คราวนี้เราก้าวไปข้างหน้า เราจะออกแบบตัวควบคุมแคชที่เชื่อมโยงชุดสี่ทางอย่างง่าย ข้อได้เปรียบ ? อัตราการพลาดน้อยกว่า แต่ในราคาประสิทธิภาพ

การออกแบบ Interrupt Controller ที่ตั้งโปรแกรมได้ใน VHDL: 4 ขั้นตอน

การออกแบบ Programmable Interrupt Controller ใน VHDL: ฉันรู้สึกท่วมท้นกับคำตอบที่ได้รับในบล็อกนี้ ขอบคุณสำหรับการเยี่ยมชมบล็อกของฉันและกระตุ้นให้ฉันแบ่งปันความรู้ของฉันกับคุณ ครั้งนี้ ฉันจะนำเสนอการออกแบบโมดูลที่น่าสนใจอื่นที่เราเห็นใน SOC ทั้งหมด -- Interrupt C

การออกแบบตัวควบคุมแคชอย่างง่ายใน VHDL: 4 ขั้นตอน

การออกแบบ Simple Cache Controller ใน VHDL: ฉันกำลังเขียนคำสั่งนี้ เพราะฉันพบว่ามันยากนิดหน่อยที่จะรับโค้ด VHDL อ้างอิงเพื่อเรียนรู้และเริ่มออกแบบตัวควบคุมแคช ดังนั้นฉันจึงออกแบบตัวควบคุมแคชด้วยตัวเองตั้งแต่เริ่มต้น และทดสอบกับ FPGA ได้สำเร็จ ฉันมีพ

PID Controller VHDL: 10 ขั้นตอน

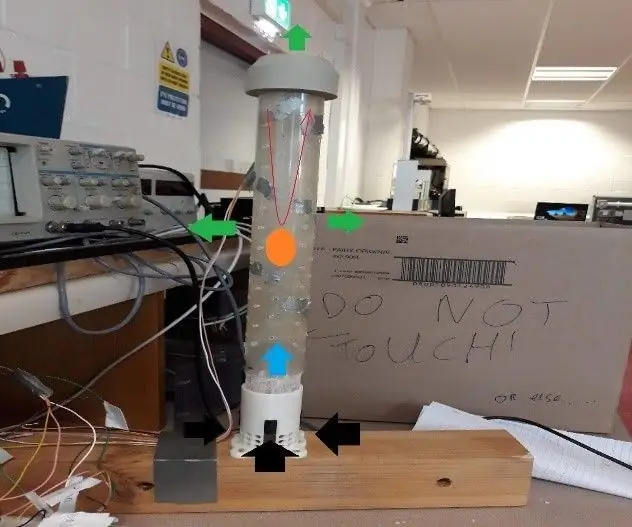

PID Controller VHDL: โครงการนี้เป็นโครงการสุดท้ายของฉันในการสำเร็จการศึกษาระดับปริญญาตรีเกียรตินิยมจาก Cork Institute of Technology บทช่วยสอนนี้แบ่งออกเป็นสองส่วน ส่วนแรกจะครอบคลุมเนื้อหาหลักของรหัส PID ซึ่งเป็นจุดประสงค์หลักของโครงการและส่วนที่สอง