สารบัญ:

- ผู้เขียน John Day day@howwhatproduce.com.

- Public 2024-01-30 13:03.

- แก้ไขล่าสุด 2025-01-23 15:12.

ในคำแนะนำนี้ เราจะอธิบายวิธีการใช้ตัวแปลงอนาล็อกเป็นดิจิตอล (ADC) 8 บิตใน SLG46855V ที่สามารถตรวจจับกระแสโหลดและเชื่อมต่อกับ MCU ผ่าน I2C การออกแบบนี้ใช้ได้กับการตรวจจับกระแสต่างๆ เช่น แอมมิเตอร์ ระบบตรวจจับข้อบกพร่อง และมาตรวัดน้ำมันเชื้อเพลิง

ด้านล่างนี้ เราได้อธิบายขั้นตอนที่จำเป็น ทำความเข้าใจว่าโซลูชันได้รับการตั้งโปรแกรมเพื่อสร้างความรู้สึกในปัจจุบันของ ADC อย่างไร อย่างไรก็ตาม หากคุณต้องการเพียงแค่ผลลัพธ์ของการเขียนโปรแกรม ให้ดาวน์โหลดซอฟต์แวร์ GreenPAK เพื่อดูไฟล์การออกแบบ GreenPAK ที่เสร็จสมบูรณ์แล้ว เสียบ GreenPAK Development Kit เข้ากับคอมพิวเตอร์ของคุณและกดโปรแกรมเพื่อสร้างความรู้สึกในปัจจุบันของ ADC

ขั้นตอนที่ 1: สถาปัตยกรรม ADC

ADC นั้นประกอบด้วยเครื่องเปรียบเทียบแอนะล็อกและตัวแปลงดิจิทัลเป็นแอนะล็อก (DAC) เครื่องเปรียบเทียบจะตรวจจับแรงดันไฟฟ้าขาเข้ากับแรงดันไฟขาออกของ DAC และต่อมาจะควบคุมว่าจะเพิ่มหรือลดรหัสอินพุต DAC หรือไม่ เพื่อให้เอาต์พุต DAC มาบรรจบกันกับแรงดันไฟฟ้าขาเข้า รหัสอินพุต DAC ที่ได้จะกลายเป็นรหัสเอาต์พุตดิจิทัล ADC

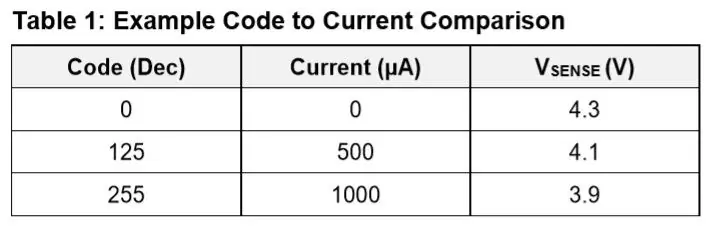

ในการใช้งานของเรา เราสร้าง DAC โดยใช้เครือข่ายตัวต้านทานแบบปรับความกว้างพัลส์ (PWM) เราสามารถสร้างเอาต์พุต PWM ที่ควบคุมแบบดิจิทัลได้อย่างแม่นยำโดยใช้ GreenPAK PWM เมื่อกรองแล้วจะกลายเป็นแรงดันอนาล็อกของเราและทำหน้าที่เป็น DAC ที่มีประสิทธิภาพ ข้อได้เปรียบที่ชัดเจนของวิธีการนี้คือ ง่ายต่อการตั้งค่าแรงดันไฟฟ้าที่สอดคล้องกับโค้ดศูนย์และเต็มสเกล (ออฟเซ็ตและเกนที่เท่ากัน) โดยเพียงแค่ปรับค่าตัวต้านทาน ตัวอย่างเช่น ผู้ใช้ต้องการอ่านรหัสศูนย์จากเซ็นเซอร์อุณหภูมิที่ไม่มีกระแส (0 µA) ที่สอดคล้องกับ 4.3 V และรหัสเต็มสเกลที่ 1,000 µA ซึ่งสอดคล้องกับ 3.9 V (ตารางที่ 1) ใช้งานได้ง่ายโดยเพียงแค่ตั้งค่าตัวต้านทานสองสามค่า การมีช่วง ADC ที่ตรงกับช่วงเซ็นเซอร์ที่สนใจ ทำให้เราใช้ความละเอียด ADC ให้เกิดประโยชน์สูงสุด

การพิจารณาการออกแบบสำหรับสถาปัตยกรรมนี้คือความถี่ PWM ภายในต้องเร็วกว่าอัตราการอัพเดต ADC มาก เพื่อป้องกันพฤติกรรม underdamed ของลูปควบคุม อย่างน้อยที่สุดควรยาวกว่านาฬิกานับข้อมูล ADC หารด้วย 256 ในการออกแบบนี้ ระยะเวลาการอัปเดต ADC ถูกตั้งค่าเป็น 1.3312 มิลลิวินาที

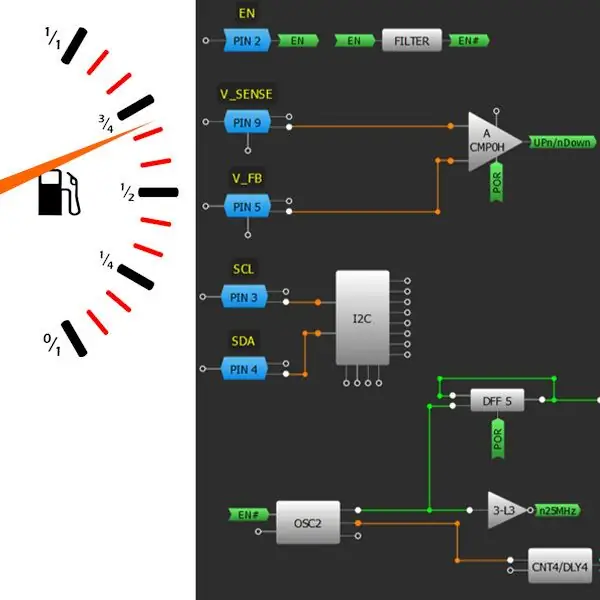

ขั้นตอนที่ 2: วงจรภายใน

ADC ที่ยืดหยุ่นขึ้นอยู่กับการออกแบบที่นำเสนอใน Dialog Semiconductor AN-1177 ความเร็วสัญญาณนาฬิกาเพิ่มขึ้นจาก 1 MHz เป็น 12.5 MHz เพื่อตอกย้ำตัวนับ ADC เนื่องจาก SLG46855 มีนาฬิกา 25 MHz ให้ใช้งาน ซึ่งช่วยให้อัตราการอัปเดตเร็วขึ้นมากสำหรับความละเอียดตัวอย่างที่ละเอียดยิ่งขึ้น LUT clocking ของนาฬิกาข้อมูล ADC มีการเปลี่ยนแปลง ดังนั้นมันจะส่งผ่านสัญญาณ 12.5 MHz เมื่อ PWM DFF ต่ำ

ขั้นตอนที่ 3: วงจรภายนอก

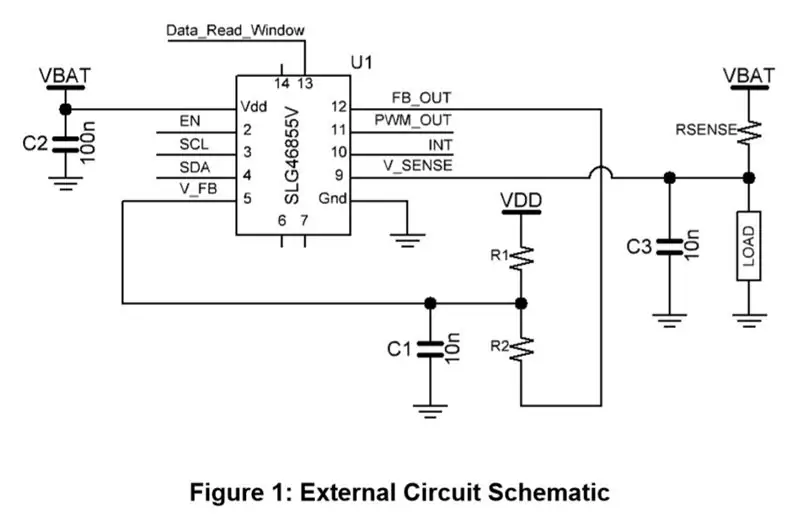

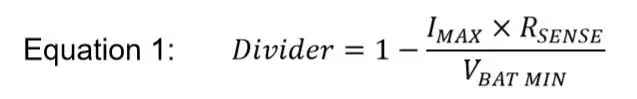

เครือข่ายตัวต้านทานและตัวเก็บประจุภายนอกใช้เพื่อแปลง PWM เป็นแรงดันอนาล็อกตามที่แสดงในแผนผังวงจรในรูปที่ 1 ค่าต่างๆ จะถูกคำนวณสำหรับความละเอียดสูงสุดสำหรับกระแสสูงสุดที่อุปกรณ์จะรับรู้ เพื่อให้เกิดความยืดหยุ่นนี้ เราจึงเพิ่มตัวต้านทาน R1 และ R2 ขนานกับ VDD และกราวด์ ตัวแบ่งตัวต้านทานแบ่ง VBAT ลงที่ด้านต่ำของช่วงแรงดันไฟฟ้า อัตราส่วนตัวหารสำหรับ VBAT ขั้นต่ำที่คาดไว้สามารถแก้ไขได้โดยใช้สมการที่ 1

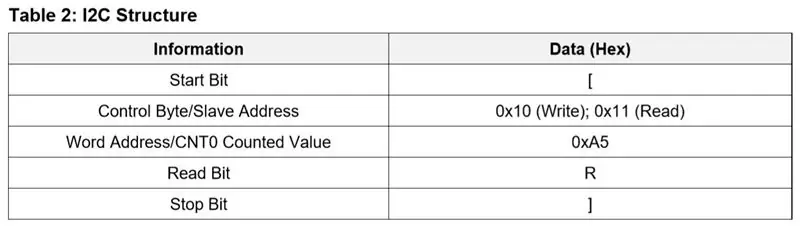

ขั้นตอนที่ 4: คำแนะนำในการอ่าน I2C

ตารางที่ 1 อธิบายโครงสร้างคำสั่ง I2C เพื่ออ่านข้อมูลที่จัดเก็บไว้ใน CNT0 คำสั่ง I2C ต้องการบิตเริ่มต้น ไบต์ควบคุม ที่อยู่คำ บิตอ่าน และบิตหยุด

ตัวอย่างคำสั่ง I2C เพื่ออ่านค่าที่นับ CNT0 นั้นเขียนไว้ด้านล่าง:

[0x10 0xA5] [0x11 R]

ค่าที่นับที่อ่านกลับจะเป็นค่ารหัส ADC ตัวอย่างเช่น รหัส Arduino จะรวมอยู่ในไฟล์ ZIP ของบันทึกการใช้งานนี้บนเว็บไซต์ของ Dialog

ขั้นตอนที่ 5: ผลลัพธ์

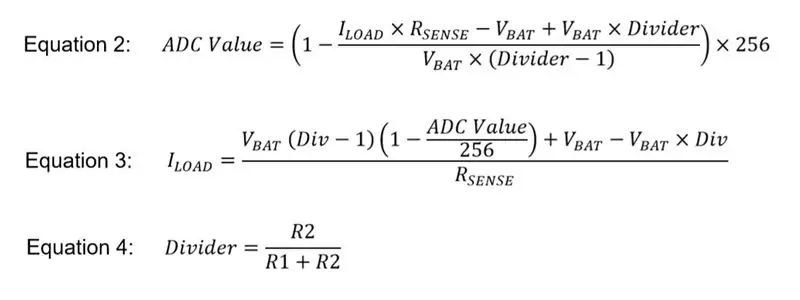

เพื่อทดสอบความแม่นยำของการออกแบบการรับรู้กระแส ADC ค่าที่วัดได้ที่กระแสโหลดที่กำหนดและระดับ VDD จะถูกนำไปเปรียบเทียบกับค่าทางทฤษฎี ค่า ADC ทางทฤษฎีคำนวณด้วยสมการ 2

ILOAD ที่สัมพันธ์กับค่า ADC จะพบได้ในสมการที่ 3

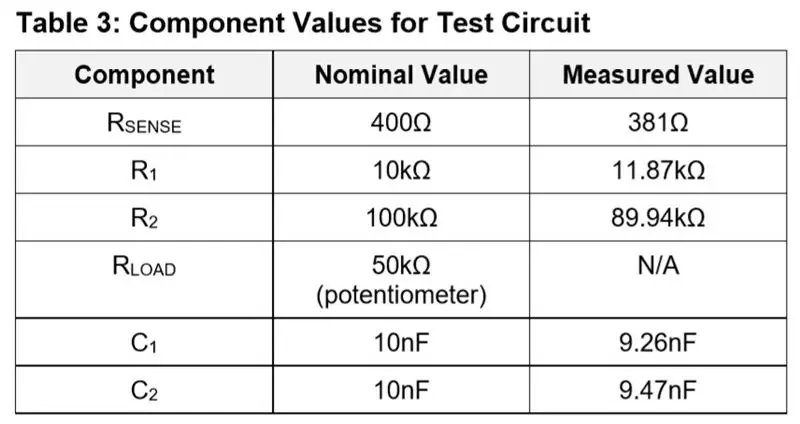

สำหรับผลลัพธ์ต่อไปนี้ ฉันใช้ค่าส่วนประกอบเหล่านี้ที่แสดงในตารางที่ 3

ความละเอียดของค่า ADC เป็นการแปลง ILOAD สามารถคำนวณได้โดยใช้สมการที่ 3 โดยมีค่าที่วัดได้ในตารางที่ 2 และตั้งค่า ADC เป็น 1 โดยที่ VBAT 3.9 V ความละเอียดจะเท่ากับ 4.96 µA/div

เพื่อเพิ่มประสิทธิภาพวงจรการรับรู้กระแส ADC ให้อยู่ในระดับ VDD ต่ำสุด 3.6 V โดยมีกระแสสูงสุด 1100 µA และตัวต้านทานความรู้สึก 381 Ω ค่าสัมประสิทธิ์ตัวหารในอุดมคติจะเท่ากับ 0.884 ตามสมการที่ 1 ด้วยค่าที่ระบุในตาราง 2 ตัวหารจริงมีค่าสัมประสิทธิ์ตัวหารที่ 0.876 เนื่องจากค่านี้น้อยกว่าเล็กน้อย จะช่วยให้ช่วงกระแสโหลดใหญ่ขึ้นเล็กน้อย ดังนั้นค่า ADC จะใกล้เคียงกับช่วงเต็มแต่จะไม่ล้น ค่าตัวหารจริงคำนวณด้วยสมการ 4

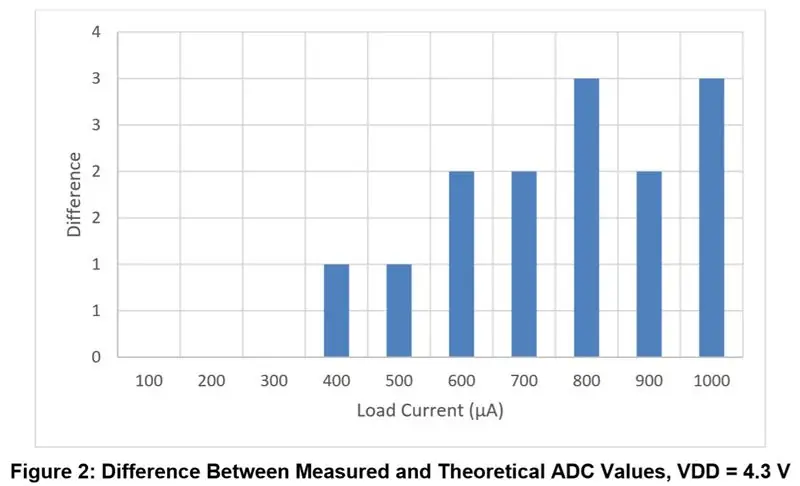

ด้านบน (รูปที่ 2-6 ตาราง 4-6) เป็นการวัดของวงจรที่ระดับแรงดันไฟฟ้าสามระดับ: 4.3 V, 3.9 V และ 3.6 V แต่ละระดับจะแสดงกราฟที่แสดงความแตกต่างระหว่างค่า ADC ที่วัดได้และตามทฤษฎี ค่าทางทฤษฎีจะถูกปัดเศษให้เป็นจำนวนเต็มใกล้เคียงที่สุด มีกราฟสรุปเพื่อเปรียบเทียบความแตกต่างที่ระดับแรงดันไฟฟ้าสามระดับ หลังจากนั้นจะมีกราฟแสดงความสัมพันธ์ระหว่างค่า ADC ทางทฤษฎีกับกระแสโหลดที่ระดับแรงดันไฟฟ้าต่างกัน

บทสรุป

อุปกรณ์ได้รับการทดสอบที่ระดับแรงดันไฟฟ้าสามระดับ: 3.6 V, 3.9 V และ 4.3 V ช่วงของแรงดันไฟฟ้าเหล่านี้จำลองแบตเตอรี่ลิเธียมไอออนแบบเต็มที่คายประจุจนถึงระดับปกติ จากระดับแรงดันไฟฟ้าสามระดับ สังเกตได้ว่าอุปกรณ์โดยทั่วไปมีความแม่นยำมากกว่าที่ 3.9 V สำหรับวงจรภายนอกที่เลือก ความแตกต่างระหว่างค่า ADC ที่วัดได้และทางทฤษฎีมีค่าทศนิยมเพียง 1 ค่าที่กระแสโหลด 700 - 1,000 µA ที่ช่วงแรงดันไฟฟ้าที่กำหนด ค่า ADC ที่วัดได้คือจุดทศนิยม 3 จุดเหนือสภาวะปกติในกรณีที่เลวร้ายที่สุด สามารถปรับเปลี่ยนตัวแบ่งตัวต้านทานเพิ่มเติมเพื่อปรับระดับแรงดันไฟฟ้า VDD ต่างๆ ให้เหมาะสมที่สุด

แนะนำ:

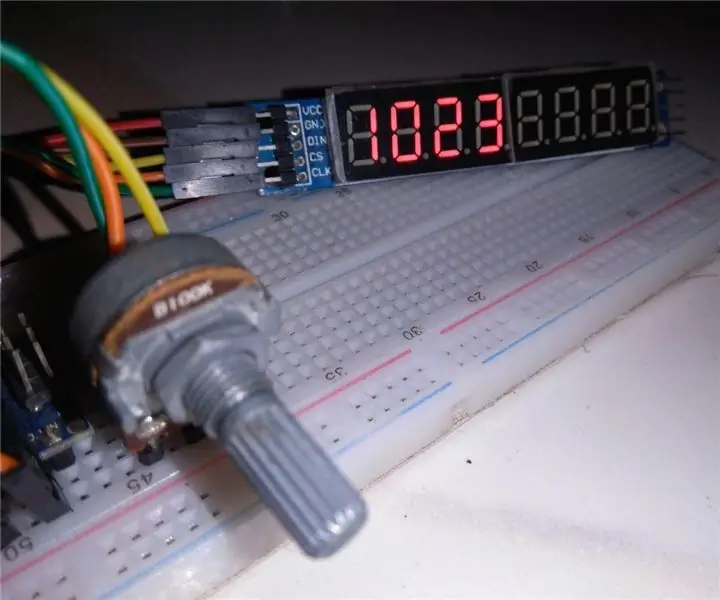

7 ส่วนเพื่อแสดงค่า ADC #Arduino, #Arduino: 4 ขั้นตอน

7-segment to Display ADC #Arduino Values, #Arduino: ในบทความนี้ ผมจะจัดทำโครงการที่ยังคงเกี่ยวข้องกับบทความก่อนหน้านี้ คือการประมวลผลข้อมูล ADC ดังนั้นคุณไม่จำเป็นต้องมีจอภาพแบบอนุกรมเพื่อดูค่าของข้อมูล ADC ในบทความนี้ฉันจะทำให้การแสดงค่า ADC Value viewer ดังนั้นคุณไม่

อ่านค่า ADC จากโพเทนชิโอมิเตอร์: 4 ขั้นตอน

อ่านค่า ADC จากโพเทนชิโอมิเตอร์: ในบทความนี้ ผมจะแสดงวิธีอ่านค่า ADC จากโพเทนชิออมิเตอร์ ซึ่งเป็นพื้นฐานของการเขียนโปรแกรม Arduino ซึ่งกำลังอ่านค่าแอนะล็อกโดยใช้พินอนาล็อกที่ Arduino จัดหาให้ นอกจากการใช้โพเทนชิโอแล้ว ยังมีเซ็นเซอร์หลายตัวที่

Arduino และ TI ADS1110 16-bit ADC: 6 ขั้นตอน

Arduino และ TI ADS1110 16 บิต ADC: ในบทช่วยสอนนี้ เราจะตรวจสอบการใช้ Arduino เพื่อทำงานร่วมกับ Texas Instruments ADS1110 ซึ่งเป็น IC ตัวแปลงอนาล็อกเป็นดิจิทัลขนาด 16 บิตที่เล็กแต่มีประโยชน์อย่างเหลือเชื่อ สามารถทำงานได้ระหว่าง 2.7 ถึง 5.5 V ดังนั้นจึงเหมาะสำหรับ Arduino Due และโวลต

Arduino และ PCF8591 ADC DAC IC: 7 ขั้นตอน

Arduino และ PCF8591 ADC DAC IC: คุณเคยต้องการพินอินพุตแบบอะนาล็อกเพิ่มเติมในโครงการ Arduino ของคุณหรือไม่ แต่ไม่ต้องการแยกออกเป็นเมก้า? หรือคุณต้องการสร้างสัญญาณอะนาล็อก? จากนั้นตรวจสอบหัวข้อของบทช่วยสอนของเรา – NXP PCF8591 IC.It แก้ปัญหาทั้งสองนี้

คุณรู้เกี่ยวกับการปรับ ESP32 ADC หรือไม่: 29 ขั้นตอน

คุณรู้เกี่ยวกับการปรับ ESP32 ADC หรือไม่: วันนี้ ฉันจะพูดถึงปัญหาทางเทคนิคเพิ่มเติม แต่สิ่งหนึ่งที่ฉันคิดว่าทุกคนที่ทำงานกับ ESP32 ควรรู้: ปัญหาของการปรับอ่าน ADC (ตัวแปลงแอนะล็อกเป็นดิจิทัล) ฉันพบว่าสิ่งนี้สำคัญเพราะเมื่อทำ "การวัด" โดยเฉพาะ