สารบัญ:

- ขั้นตอนที่ 1: สร้างโมดูล PWM- ไฟล์ต้นทาง

- ขั้นตอนที่ 2: การสร้างโมดูล PWM- การตั้งค่า Vivado

- ขั้นตอนที่ 3: การสร้างโมดูล PWM- สร้างไฟล์โครงการ

- ขั้นตอนที่ 4: การสร้างโมดูล PWM - การออกแบบบล็อกและการตั้งค่าไฟล์ข้อ จำกัด (I)

- ขั้นตอนที่ 5: การสร้างโมดูล PWM - การออกแบบบล็อกและการตั้งค่าไฟล์ข้อ จำกัด (II)

- ขั้นตอนที่ 6: การสร้างโมดูล PWM - การออกแบบบล็อกและการตั้งค่าไฟล์ข้อ จำกัด (III)

- ขั้นตอนที่ 7: การสร้างโมดูล PWM - การออกแบบบล็อกและการตั้งค่าไฟล์ข้อ จำกัด (IV)

- ขั้นตอนที่ 8: การสร้างโมดูล PWM - การออกแบบบล็อกและการตั้งค่าไฟล์ข้อ จำกัด (V)

- ขั้นตอนที่ 9: การสร้างโมดูล PWM- การติดตั้งฮาร์ดแวร์

- ขั้นตอนที่ 10: การสร้างโมดูล PWM- สร้าง Bitstream และเปิดใช้ SDK

- ขั้นตอนที่ 11: การสร้างโมดูล PWM- สร้างแอปพลิเคชันใหม่ใน Xilinx SDK

- ขั้นตอนที่ 12: การสร้างโมดูล PWM- ภาพรวมของ Project Explorer (I)

- ขั้นตอนที่ 13: การสร้างโมดูล PWM- ภาพรวมของ Project Explorer (II)

- ขั้นตอนที่ 14: การสร้างโมดูล PWM- ภาพรวมของ Project Explorer (III)

- ขั้นตอนที่ 15: การสร้างโมดูล PWM- สรุปฟังก์ชัน PWM (I)

- ขั้นตอนที่ 16: การสร้างโมดูล PWM- สรุปฟังก์ชัน PWM (II)

- ขั้นตอนที่ 17: การสร้างโมดูล PWM- สรุปฟังก์ชัน PWM (III)

- ขั้นตอนที่ 18: การสร้างโมดูล PWM- ทำให้ใช้งานได้

- ขั้นตอนที่ 19: สตรีมการประมวลผลวิดีโอบน Digilent ZYBO ด้วย OV7670

- ขั้นตอนที่ 20: บล็อกไดอะแกรมให้สมบูรณ์

- ขั้นตอนที่ 21: เชื่อมต่อ OV7670 กับ ZYBO

- ขั้นตอนที่ 22: สร้างการออกแบบบล็อก

- ขั้นตอนที่ 23: เพิ่มไฟล์ VHDL สำหรับ OV7670 Camera Control and Capture

- ขั้นตอนที่ 24: เพิ่มไฟล์ข้อจำกัด

- ขั้นตอนที่ 25: เพิ่ม IP Repo สำหรับ HLS IP

- ขั้นตอนที่ 26: เพิ่มโมดูลและ IP

- ขั้นตอนที่ 27: การตั้งค่าการกำหนดค่า IP

- ขั้นตอนที่ 28: เพิ่มและกำหนดค่า PS IP Block

- ขั้นตอนที่ 29: ส่วนที่ 1 การสร้างโมดูล PWM สำหรับเซอร์โวมอเตอร์

- ขั้นตอนที่ 30: การเชื่อมต่อด้านอินพุตวิดีโอ (เน้น alkk)

- ขั้นตอนที่ 31: การเชื่อมต่อกับ OV7670

- ขั้นตอนที่ 32: การเชื่อมต่อกับ Video Out Side

- ขั้นตอนที่ 33: เรียกใช้บล็อกและการเชื่อมต่ออัตโนมัติ

- ขั้นตอนที่ 34: สร้าง HDL Wrapper

- ขั้นตอนที่ 35: สร้าง Bitstream, ส่งออกฮาร์ดแวร์ไปยัง SDK, เปิด SDK จาก Vivado

- ขั้นตอนที่ 36: SDK (ไม่มี FreeRTOS)

- ขั้นตอนที่ 37: การใช้งาน FreeRTOS

- ขั้นตอนที่ 38: คำแนะนำการใช้งาน

- ขั้นตอนที่ 39: ข้อมูลอ้างอิงและลิงก์

- ผู้เขียน John Day day@howwhatproduce.com.

- Public 2024-01-30 13:07.

- แก้ไขล่าสุด 2025-01-23 15:12.

เริ่มที่ขั้นตอนที่หนึ่งเพื่อดูรายละเอียดเกี่ยวกับการสร้างตัวควบคุมเซอร์โว PWM แบบ 2 แกน

เริ่มต้นที่แผนภาพบล็อกขนาดใหญ่ (ขั้นตอนที่ 19) สำหรับโครงการทั้งหมด

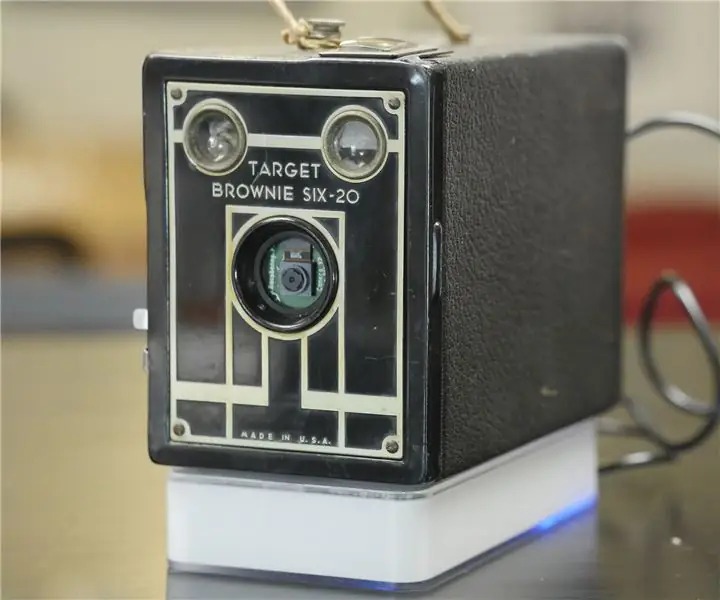

การตั้งค่ากล้อง + แพน/เอียงที่เราใช้:

PmodCON3 จาก Digilent ใช้เพื่อเชื่อมต่อเซอร์โว

ขั้นตอนที่ 1: สร้างโมดูล PWM- ไฟล์ต้นทาง

ขั้นตอนที่ 2: การสร้างโมดูล PWM- การตั้งค่า Vivado

ขั้นแรก ดาวน์โหลด Vivado Design Suite จากเว็บไซต์ Xilinx ติดตั้งชุดการออกแบบทั้งหมด รวมถึง Vivado Software Development Kit (SDK) โครงการนี้ใช้เวอร์ชัน 2017.2

ในระหว่างนี้ ควรติดตั้ง Digilent Adept 2 เป็นไดรเวอร์บอร์ด Zybo

ขั้นตอนที่ 3: การสร้างโมดูล PWM- สร้างไฟล์โครงการ

ก่อนสร้างไฟล์โครงการ คุณควรตรวจสอบให้แน่ใจว่าคุณได้ติดตั้งไฟล์ Zybo อย่างถูกต้องตามบทช่วยสอนที่นี่:

Vivado เวอร์ชัน 2015.1 และใหม่กว่าการติดตั้งไฟล์บอร์ด

เปิด Vivado 2017.2 ในการเริ่มต้นอย่างรวดเร็ว ให้คลิกที่ สร้างโครงการ -> ถัดไป -> ชื่อโครงการ (ตั้งชื่อโครงการของคุณที่นี่) -> ประเภทโครงการ ในประเภทโครงการ ให้เลือกโครงการ RTL และทำเครื่องหมายที่ "ไม่ต้องระบุแหล่งที่มาในเวลานี้" ถัดไป สำหรับส่วนเริ่มต้น เลือก "บอร์ด" และ "Zybo" เป็นชื่อที่แสดง ถัดไป คลิกเสร็จสิ้นเพื่อเริ่มโครงการ

ขั้นตอนที่ 4: การสร้างโมดูล PWM - การออกแบบบล็อกและการตั้งค่าไฟล์ข้อ จำกัด (I)

บน Flow Navigator คลิกที่ “”สร้างการออกแบบบล็อก” จากนั้นกดตกลง คลิกเครื่องหมาย “+” เพื่อเพิ่ม IP ที่จำเป็น เพิ่ม:

- ระบบประมวลผล ZYNQ7 หนึ่งระบบ ตัวจับเวลา AXI สองตัว

- ตัวจับเวลา AXI สองตัว

ขั้นตอนที่ 5: การสร้างโมดูล PWM - การออกแบบบล็อกและการตั้งค่าไฟล์ข้อ จำกัด (II)

หลังจากเพิ่ม IP แล้ว ให้เรียกใช้ Block Automation และการเชื่อมต่ออัตโนมัติ เมื่อการทำงานอัตโนมัติเสร็จสิ้น บนบล็อก “axi_timer_0” ให้คลิกขวาที่ pwm0 -> Make External ตั้งชื่อพินภายนอก pwm0 เป็น pwm_Xaxis ทำซ้ำขั้นตอนข้างต้นบนบล็อก “axi_timer_1” และตั้งชื่อพินภายนอก pwm0 เป็น pwm_Zaxis

ขั้นตอนที่ 6: การสร้างโมดูล PWM - การออกแบบบล็อกและการตั้งค่าไฟล์ข้อ จำกัด (III)

สังเกตว่าทุกครั้งที่เราออกแบบบล็อกใน Vivado เสร็จ เราจำเป็นต้องสร้าง HDL Wrapper เนื่องจากจะเป็นโมดูลระดับบนสุดสำหรับแต่ละโครงการ

ขั้นตอนที่ 7: การสร้างโมดูล PWM - การออกแบบบล็อกและการตั้งค่าไฟล์ข้อ จำกัด (IV)

ตอนนี้ เราต้องตั้งค่าไฟล์ข้อจำกัดของเราเพื่อกำหนดพินที่เชื่อมต่อกับบล็อกไดอะแกรมของเรา ปิดหน้าต่าง Block Design, บนแท็บ Sources, “Add Sources”->Add or create constraints-> เพิ่ม Zybo-Master.xdc เป็นไฟล์ข้อจำกัดของเรา

ขั้นตอนที่ 8: การสร้างโมดูล PWM - การออกแบบบล็อกและการตั้งค่าไฟล์ข้อ จำกัด (V)

เปิดไฟล์ข้อ จำกัด Zybo-Master.xdc จากโฟลเดอร์ Constraints ยกเลิกการใส่เครื่องหมายพอร์ตที่เราต้องการระบุเป็นสัญญาณเอาท์พุตและเปลี่ยนชื่อ "get_ports{XXXX}" ซึ่ง XXXX หมายถึงพินภายนอกที่มีชื่ออยู่ในแผนภาพบล็อก การตั้งค่าของไฟล์ข้อ จำกัด จะแสดงในรูป

ขั้นตอนที่ 9: การสร้างโมดูล PWM- การติดตั้งฮาร์ดแวร์

เชื่อมต่อเซอร์โวมอเตอร์กับ Pmod CON3 TowerPro SG90 เป็นรุ่นเซอร์โวมอเตอร์ที่เราใช้ในโครงการนี้ สำหรับสายเซอร์โวมอเตอร์ สายสีส้มแทนสัญญาณ PWM ซึ่งเชื่อมต่อกับพิน SIG ใน Pmod CON3 สายสีแดง Vcc เป็นสายไฟที่เชื่อมต่อกับขา VS ใน Pmod CON3 ในที่สุดสายสีน้ำตาล Gnd เป็นสายกราวด์ที่เชื่อมต่อกับพิน GND ถัดไป ใส่ Pmod CON3 ไปที่แถวบนของพอร์ต JD ใน Zybo Board

ขั้นตอนที่ 10: การสร้างโมดูล PWM- สร้าง Bitstream และเปิดใช้ SDK

1. ในแท็บ Project Navigator ให้เรียกใช้ Generate BitStream

2. ส่งออกฮาร์ดแวร์: ไฟล์ > ส่งออก > ส่งออกฮาร์ดแวร์-> ทำเครื่องหมายที่ "รวมบิตสตรีม" -> ตกลง 3. เปิด SDK: ไฟล์ -> เปิด SDK

ขั้นตอนที่ 11: การสร้างโมดูล PWM- สร้างแอปพลิเคชันใหม่ใน Xilinx SDK

สร้างแอปพลิเคชันใหม่:

ไฟล์ > ใหม่ > โครงการแอปพลิเคชัน -> ป้อนชื่อโครงการของคุณ -> เสร็จสิ้น

ภายใต้ Project Explorer ควรมีสามโฟลเดอร์

ในกรณีนี้ “design_1_wrapper_hw_platform_0” เป็นโฟลเดอร์ที่ Vivado ส่งออกไปก่อนหน้านี้ Axis_2_PWM_SDK_bsp เป็นโฟลเดอร์แพ็คเกจสนับสนุนบอร์ด และ Axis_2_PWM_SDK คือโฟลเดอร์โครงการหลักของเราใน SDK คุณสามารถดูไฟล์ “helloworld.c” ได้ในโฟลเดอร์ “src” ของ Axis_2_PWM_SDK โดยที่ “helloworld.c” เป็นไฟล์หลัก

ขั้นตอนที่ 12: การสร้างโมดูล PWM- ภาพรวมของ Project Explorer (I)

มาตรวจสอบไฟล์บางไฟล์ภายใต้ Project Explorer ขั้นแรก ในโฟลเดอร์ “design_1_wrapper_hw_platform_0” ให้เปิด “system.hdf” ไฟล์นี้สาธิตแผนผังที่อยู่สำหรับโปรเซสเซอร์ ps7_cortex9 และบล็อก IP ที่มีอยู่ในการออกแบบของเรา

ขั้นตอนที่ 13: การสร้างโมดูล PWM- ภาพรวมของ Project Explorer (II)

จากนั้น ตรวจสอบไฟล์ "รวม" และ "libsrc" ใต้โฟลเดอร์ "Axis_2_PWM_SDK_bsp" ไฟล์ไลบรารีที่นี่ช่วยให้เราสามารถโต้ตอบกับอุปกรณ์ต่อพ่วงฮาร์ดแวร์โดยไม่ต้อง "เล่น" การลงทะเบียน

ขั้นตอนที่ 14: การสร้างโมดูล PWM- ภาพรวมของ Project Explorer (III)

ผ่านเอกสารประกอบ BSP พบ xtmrctr.h เป็น Xilinx Timer Control Library ที่เกี่ยวข้องกับ AXI Timer โดยทั่วไป เราสามารถค้นหาฟังก์ชัน PWM ที่ต้องการได้ที่นี่ อย่างไรก็ตาม หากคุณอ่านเอกสารประกอบ “tmrctr_v4_3” แสดงว่าไดรเวอร์ไม่รองรับการทำงานของ PWM ของอุปกรณ์ในขณะนี้ เนื่องจากข้อบกพร่องในฟังก์ชัน PWM เราจึงต้องสรุปฟังก์ชัน PWM ของเราด้วยความช่วยเหลือของ xtmrctr.h และ AXI Timer v2.0 LogiCORE IP Product Guide

ขั้นตอนที่ 15: การสร้างโมดูล PWM- สรุปฟังก์ชัน PWM (I)

กลับไปที่ไฟล์หลัก “helloworld.c” รวมไฟล์ส่วนหัวต่อไปนี้:

ขั้นตอนที่ 16: การสร้างโมดูล PWM- สรุปฟังก์ชัน PWM (II)

กำหนดที่อยู่ฐานของ AXI TImer สองตัวผ่าน “xparameters.h”

ขั้นตอนที่ 17: การสร้างโมดูล PWM- สรุปฟังก์ชัน PWM (III)

สร้างฟังก์ชัน PWM ที่ต้องการ

Duty_val: แปลงค่าดีกรีเป็นรอบการทำงานPWM_Freq_Duty: ตั้งค่าความถี่และรอบการทำงานที่ต้องการเพื่อสร้าง PWM ควรกำหนดช่วงเวลานาฬิกาด้วย

PWM_START: กำหนดที่อยู่การลงทะเบียน PWM และเริ่มสร้าง PWM

PWM_STOP: กำหนดที่อยู่การลงทะเบียน PWM และหยุดการสร้าง PWM

รหัสสาธิตที่เหลือจะแสดงใน “helloworld.c” ภายใต้ “Axis_2_PWM_SDK”

ขั้นตอนที่ 18: การสร้างโมดูล PWM- ทำให้ใช้งานได้

1.โปรแกรม FPGA ผ่าน SDK

- เชื่อมต่อ Zybo Board ผ่านพอร์ต USB กับพีซี

- เครื่องมือ Xilinx -> โปรแกรม FPGA

2.เรียกใช้โปรแกรม

คลิกที่ไอคอน "Run" และเลื่อนลงเมนู -> Run As -> Launch on Hardware

3. SDK เทอร์มินัล

- เปิด SDK Terminal -> เชื่อมต่อกับ Serial Port -> OK

- เรียกใช้โปรแกรม หากโค้ดสาธิตทำงานสำเร็จ คุณควรเห็น "การเริ่มต้นเสร็จสิ้น!" บนเทอร์มินัล SDK

ขั้นตอนที่ 19: สตรีมการประมวลผลวิดีโอบน Digilent ZYBO ด้วย OV7670

แนบไฟล์เก็บถาวรที่สมบูรณ์

ขั้นตอนที่ 20: บล็อกไดอะแกรมให้สมบูรณ์

นี่แสดงไดอะแกรมที่สมบูรณ์ของการเชื่อมต่อและบล็อก IP ทั้งหมดในโปรเจ็กต์

ขั้นตอนที่ 21: เชื่อมต่อ OV7670 กับ ZYBO

สร้างการเชื่อมต่อเพื่อต่อสายโมดูล ov7670 กับ ZYBO Pmods

Data Pmod คือ Pmod D

การควบคุม Pmod คือ Pmod C

นอกจากนี้ ให้เชื่อมต่อ PmodCON3 และเซอร์โวตามที่ระบุไว้ในครึ่งแรกของบทช่วยสอนนี้

ขั้นตอนที่ 22: สร้างการออกแบบบล็อก

ใน Flow Navigator ให้คลิกที่ "สร้างการออกแบบบล็อก" จากนั้นกดตกลง

ขั้นตอนที่ 23: เพิ่มไฟล์ VHDL สำหรับ OV7670 Camera Control and Capture

เพิ่มไฟล์ VHDL ที่แนบมากับขั้นตอนนี้ในโปรเจ็กต์

ขั้นตอนที่ 24: เพิ่มไฟล์ข้อจำกัด

เพิ่มไฟล์ข้อจำกัดที่แนบมากับโปรเจ็กต์ของคุณ

ขั้นตอนที่ 25: เพิ่ม IP Repo สำหรับ HLS IP

นำไฟล์ Zip ที่แนบมาและคลายซิปลงในโฟลเดอร์ใหม่ที่มีชื่อคล้ายกันในไดเรกทอรีใหม่ (โฟลเดอร์) ชื่อ "HLS_repo"

เพิ่มที่เก็บ IP ให้กับโปรเจ็กต์ของคุณโดยไปที่แค็ตตาล็อก IP แล้วคลิกขวาเลือก "เพิ่มที่เก็บ…"

ไปที่ไดเร็กทอรี "HLS_repo" และเลือก

ไม่บังคับ: สร้างบล็อกการประมวลผลวิดีโอ HLS สำหรับตัวคุณเอง!

ขั้นตอนที่ 26: เพิ่มโมดูลและ IP

เพิ่มโมดูล ov7670_axi_stream_capture, debounce และ ov7670_controller ลงในบล็อกไดอะแกรมโดยคลิกขวาที่พื้นหลังและเลือก "เพิ่มโมดูล…"

ในทำนองเดียวกัน เพิ่ม IPs:

- HLS_Video_Track

- การเขียนบัฟเฟอร์เฟรมวิดีโอ

- อ่านบัฟเฟอร์เฟรมวิดีโอ

- ตัวควบคุมเวลาวิดีโอ

- AXI4-สตรีมไปยังวิดีโอเอาท์

- 3 ของ "ชิ้น"

- คงที่

- 2 ของ AXI Timer

ขั้นตอนที่ 27: การตั้งค่าการกำหนดค่า IP

ตามภาพ

ขั้นตอนที่ 28: เพิ่มและกำหนดค่า PS IP Block

เพิ่มระบบประมวลผล ZYNQ7 ลงในบล็อกไดอะแกรม

แก้ไขการกำหนดค่า:

-

การกำหนดค่า PS-PL

-

HP

- เปิดใช้งาน S HP 0

- เปิดใช้งาน S HP 1

-

-

การกำหนดค่านาฬิกา

-

นาฬิกาผ้า PL

- FCLK_0 ที่ 100MHz

- FCLK_1 ที่ 25MHz (OutputClock)

- FLCK_2 ที่ 35MHz (<=50MHz) (CameraClock)

-

ขั้นตอนที่ 29: ส่วนที่ 1 การสร้างโมดูล PWM สำหรับเซอร์โวมอเตอร์

นำ axi_timer_0 pwm0 ออกไปยังพอร์ตเอาต์พุตใหม่ pwm_Xaxis

นำ axi_timer_1 pwm0 ออกไปยังพอร์ตเอาต์พุตใหม่ pwm_Zaxis

ขั้นตอนที่ 30: การเชื่อมต่อด้านอินพุตวิดีโอ (เน้น alkk)

เชื่อมต่อบล็อก IP ด้านอินพุตวิดีโออย่างถูกต้อง

(* การเชื่อมต่อเหล่านี้ควรสร้างขึ้นโดยเลือกตัวเลือกที่เหมาะสมระหว่างการเชื่อมต่ออัตโนมัติ)"aclk" จาก axi_stream_capture ไปที่:

- ap_clk ในการเขียนบัฟเฟอร์เฟรมวิดีโอ

- ap_clk บนบล็อกการประมวลผลสตรีมวิดีโอ HLS

- *aclk บน AXI smartconnect IP จาก Video Frame Buffer เขียนไปยัง S_AXI_HP0

- *aclk ที่สอดคล้องกับแชนเนลของ AXI Interconnect IP สำหรับแชนเนล S_AXI ของบล็อกการประมวลผลวิดีโอ HLS และบัฟเฟอร์เฟรมวิดีโอเขียน S_AXI_HP0_ACLK บนบล็อก PS

สัญญาณสตรีมวิดีโอเชื่อมต่อแบบอนุกรมจากบล็อกการจับภาพไปยังอินเทอร์เฟซหน่วยความจำ Zynq

- วิดีโอเปลี่ยนจากบล็อกการจับภาพเป็นบล็อกการประมวลผล HLS

- วิดีโอที่ประมวลผลจากบล็อก HLS ไปที่บล็อกการเขียนบัฟเฟอร์เฟรม

- *บล็อกการเขียนบัฟเฟอร์เฟรมเชื่อมต่อกับอินเทอร์เฟซ HP0 บนบล็อก Zynq PS

- สัญญาณ m_axis_tuser จากเอาต์พุตของบล็อกการดักจับถูกต่อเข้ากับทั้งสัญญาณอินพุต video_in_TUSER บนบล็อกการประมวลผล HLS และสัญญาณ ap_start บนบล็อกเดียวกันด้วยตนเอง

สัญญาณ TUSER(tuser) ถูกใช้โดยโปรโตคอลสตรีมวิดีโอ AXI เพื่อระบุจุดเริ่มต้นของเฟรมของวิดีโอ AP_Start บอกให้บล็อก HLS เริ่มการประมวลผล ดังนั้นเราจึงใช้ tuser เพื่อทริกเกอร์บล็อก HLS เพื่อประมวลผลแต่ละเฟรม เข้ามา เมื่อเชื่อมต่อสัญญาณเดียวของบัสและแยกออกในลักษณะนี้ จำเป็นต้องเชื่อมต่อกับจุดสิ้นสุดปกติของส่วนที่เหลือของรถบัสด้วย Vivado ถือว่าถ้าคุณกำลังเชื่อมต่อสัญญาณด้วยตนเองว่าคุณต้องการตัดการเชื่อมต่อสิ่งที่ปกติจะเชื่อมต่อ

การตั้งค่าการกำหนดค่าของบล็อก IP:

บัฟเฟอร์เฟรมวิดีโอเขียน:

รูปแบบวิดีโอ: RGB8

1 ตัวอย่างต่อนาฬิกา คอลัมน์สูงสุด: 1280 (>=640) แถวสูงสุด: 960 (>=480) ความกว้างข้อมูลสูงสุด: 8

ขั้นตอนที่ 31: การเชื่อมต่อกับ OV7670

บนบล็อก ov7670_axi_stream_capture

- ทำให้อินพุตทั้งหมดภายนอก (คลิกขวาบนหมุดและเลือกจากเมนู หรือคลิกซ้าย->ctrl+T)

- ทิ้งชื่อไว้เหมือนเดิม

บนบล็อก ov7670_controller

- สร้างเอาต์พุตบล็อกทั้งหมดภายนอก

- เปลี่ยนชื่อพอร์ต config_finished เป็น led0

- เชื่อมต่อ clk กับ CameraClock (<=50MHz) (FCLK_2)

บนบล็อก debounce

- เชื่อมต่ออินพุต button1 กับพอร์ตอินพุตภายนอกที่เรียกว่า btn0

- เชื่อมต่อ out1 กับสายส่งซ้ำบนบล็อก IP ov7670_controller

- เชื่อมต่ออินพุต button2 กับพอร์ตอินพุตภายนอกที่เรียกว่า btn3

- เชื่อมต่อ out2n กับอินพุต ext_reset_in บน IP รีเซ็ตระบบโปรเซสเซอร์สำหรับโดเมนนาฬิกาจับภาพวิดีโอ (*อาจต้องทำหลังจากสร้าง IP นั้นแล้ว*)

- เชื่อมต่อ clk กับ CameraClock (<=50MHz) (FCLK_2)

ขั้นตอนที่ 32: การเชื่อมต่อกับ Video Out Side

การเชื่อมต่อสำหรับบล็อค Video Timing Controller (VTC), AXI4-Stream to Video Out และ slices

- ใช้นาฬิกา 25MHz (FCLK_1) สำหรับ vid_io_out_clk และ VTC clk

- ใช้นาฬิกา 100MHz (FCLK_0) สำหรับ alk บน AXI4-Stream to Video Out

- vtiming_out เป็น vtiming_in

- บัฟเฟอร์เฟรมวิดีโออ่าน m_axis_video ไปที่ AXI4-Stream ไปยัง Video Out video_in

- vtg_ce ไปที่ gen_clken

- ผูก VTC clken, aclken, vid_io_out_ce กับ Constant dout[0:0]

- นำ vid_hsync และ vid_vsync ออกไปยังพอร์ตเอาต์พุตภายนอก vga_hs และ vga_vs ตามลำดับ (ไม่มีภาพ)

ชิ้น:

-

ควรตั้งค่าสไลซ์ตามภาพที่แนบมา

- เปลี่ยนชื่อบล็อกเป็น slice_red, slice_green และ slice_blue

- ตั้งค่าช่วงสไลซ์ตามที่แสดงในภาพตามชื่อบล็อก

- เชื่อมต่อแต่ละเอาต์พุตของสไลซ์กับเอาต์พุตพอร์ตภายนอกตามที่แสดงในภาพ

- vid_data[23:0] เชื่อมต่อกับอินพุตสำหรับแต่ละสไลซ์ (Din[23:0])

ขั้นตอนที่ 33: เรียกใช้บล็อกและการเชื่อมต่ออัตโนมัติ

เรียกใช้ Block Automation เพื่อเชื่อมต่อสิ่งต่างๆ จากบล็อก ZYNQ7 PS ตามที่แสดงตามภาพ

เรียกใช้การเชื่อมต่ออัตโนมัติเพื่อสร้าง IP การเชื่อมต่อโครงข่ายทั้งหมด ใส่ใจกับตัวเลือกทั้งหมดในแต่ละภาพ

บนบล็อก debounce ให้เชื่อมต่อ out2n กับโดเมนนาฬิกาจับภาพวิดีโอ รีเซ็ตระบบโปรเซสเซอร์ ext_reset_in อินพุต

ขั้นตอนที่ 34: สร้าง HDL Wrapper

สร้าง HDL Wrapper สำหรับการออกแบบบล็อกของคุณ

ตั้งเป็นโมดูลด้านบน

ขั้นตอนที่ 35: สร้าง Bitstream, ส่งออกฮาร์ดแวร์ไปยัง SDK, เปิด SDK จาก Vivado

ตรวจสอบให้แน่ใจว่าได้รวมบิตสตรีมในการส่งออก

การสร้างบิตสตรีมอาจใช้เวลานานมาก

จากนั้นเปิด SDK

ขั้นตอนที่ 36: SDK (ไม่มี FreeRTOS)

เวอร์ชันนี้ทำทุกอย่างโดยไม่ต้องใช้ FreeRTOS ซึ่งย่อโค้ดให้สวยงาม

สร้าง BSP แบบสแตนด์อโลนตามการออกแบบฮาร์ดแวร์ ตัวเลือกเริ่มต้นควรจะใช้ได้ ตรวจสอบให้แน่ใจว่าได้สร้างแหล่ง BSP แล้ว

สร้าง App ตามภาพ (ใบสมัครเปล่า)

ลบหลักที่สร้างอัตโนมัติและนำเข้าไฟล์ที่แนบมา

ขั้นตอนที่ 37: การใช้งาน FreeRTOS

เวอร์ชันนี้ใช้ FreeRTOS สร้าง FreeRTOS901 BSP ตามการออกแบบฮาร์ดแวร์ ตัวเลือกเริ่มต้นควรจะใช้ได้ ตรวจสอบให้แน่ใจว่าได้สร้างแหล่ง BSP แล้ว

สร้าง App ตามภาพ (ใบสมัครเปล่า)

ลบหลักที่สร้างอัตโนมัติและนำเข้าไฟล์ที่แนบมา

ขั้นตอนที่ 38: คำแนะนำการใช้งาน

โครงการนี้ค่อนข้างยุ่งยากในการทำงาน ทำตามขั้นตอนตามลำดับ

ตรวจสอบให้แน่ใจว่า ZYBO ของคุณไม่ได้โหลดอะไรเลยเมื่อเปิดเครื่อง ซึ่งหมายความว่าไฟ LED เสร็จสิ้นไม่ควรสว่างขึ้น วิธีหนึ่งในการทำเช่นนี้คือตั้งค่าจัมเปอร์แหล่งบูตเป็น JTAG

เปิดโครงการ (FreeRTOS หรือไม่) ที่คุณต้องการตั้งโปรแกรมจาก SDK

- เปิด ZYBO ของคุณ ไฟ LED ที่เสร็จสิ้นไม่ควรสว่างขึ้น

- ตั้งโปรแกรม FPGA ด้วยไฟล์บิต ไฟ LED ที่เสร็จสิ้นควรสว่างขึ้น Led0 ไม่ควรสว่างขึ้น

- รันโค้ด (อย่าลืมว่าต้องผ่านจุดพักเริ่มต้นหากคุณกำลังดำเนินการนั้น)

ณ จุดนี้คุณควรได้รับเอาต์พุตบนจอแสดงผล VGA ของคุณ

ในการรีสตาร์ท (หากมีข้อบกพร่องหรืออะไรก็ตาม): ให้แตะปุ่ม PS-SRST อย่างรวดเร็วหรือปิด ZYBO แล้วเปิดใหม่อีกครั้ง ดำเนินการต่อจากขั้นตอนที่ 2

การหยุดโปรเซสเซอร์ด้วยดีบักเกอร์จะทำให้กล้องอยู่ในตำแหน่งที่ค้างไว้แทนที่จะเคลื่อนที่ สตรีมวิดีโอจะดำเนินต่อไป

ขั้นตอนที่ 39: ข้อมูลอ้างอิงและลิงก์

คู่มืออ้างอิงและเอกสารอ้างอิงของ Xilinx:

- PG044 - สตรีม AXI ไปยังวิดีโอเอาท์

- PG278 - บัฟเฟอร์เฟรมวิดีโออ่าน/เขียน

ลิงค์อื่นๆ:

- บล็อกของ Lauri - อินพุต VDMA

- บล็อกของ Lauri - เอาต์พุต OV7670 เป็น VGA โดยใช้BRAM

- Hamsterworks wiki โดย Mike Fields แหล่งที่มาดั้งเดิมของรหัส OV7670

- เอกสารข้อมูลแสดงข้อกำหนดเกี่ยวกับเวลาพื้นฐาน

แนะนำ:

กล้อง Retro Raspberry Pi Tumblr GIF: 10 ขั้นตอน (พร้อมรูปภาพ)

กล้อง Retro Raspberry Pi Tumblr GIF: ฉันต้องการวิธีใช้กล้องวินเทจของฉันในรูปแบบดิจิทัลใหม่ ฉันมีไม่กี่คนที่เล่นในสภาวะต่างๆ แต่ไม่ได้ใช้มานานแล้วเพราะภาพยนตร์เรื่องนี้มีค่าใช้จ่ายสูงในการพัฒนา ปฏิบัติตามคำแนะนำนี้เพื่อดูว่าฉันใส่ Raspberry

กล้อง Arduino Bluetooth: 4 ขั้นตอน (พร้อมรูปภาพ)

Arduino Bluetooth Camera: สวัสดี! วันนี้คุณแทบจะทำให้ทุกคนประหลาดใจกับโทรศัพท์มือถือที่มีกล้อง อุปกรณ์ไร้สาย และความก้าวหน้าทางเทคนิคอื่นๆ ด้วยแพลตฟอร์ม Arduino ผู้คนนับล้านได้ค้นพบโลกมหัศจรรย์ของอุปกรณ์อิเล็กทรอนิกส์และการเขียนโปรแกรม 100,5

กล้อง 3d Fpv ราคาประหยัดสำหรับ Android: 7 ขั้นตอน (พร้อมรูปภาพ)

กล้อง 3d Fpv ราคาประหยัดสำหรับ Android: FPV เป็นสิ่งที่เจ๋งมาก และจะดีกว่าใน 3 มิติ มิติที่สามไม่สมเหตุสมผลนักในระยะทางไกล แต่สำหรับ Micro Quadcopter ในร่มนั้นสมบูรณ์แบบ ดังนั้นฉันจึงดูที่ตลาด แต่กล้องที่ฉันพบก็เหมือนกันเขา

กล้อง High Five: 9 ขั้นตอน (พร้อมรูปภาพ)

High Five Camera: ฉันบอกความลับกับคุณได้ไหม ฉันไม่ชอบการจับมือ ฉันไม่ได้จริงๆ การจับมือทำให้ฉันรู้สึกสกปรก มันไม่มีตัวตนเกินไป มันเป็นท่าทางที่ไม่มีจิตวิญญาณและกลิ่นของนิติบุคคล เหตุใดเราจึงต้องจำกัดตัวเองให้อยู่ในปฏิสัมพันธ์ที่น่าเบื่อเพียงครั้งเดียวนี้

รถโมเดล RC เอียง: 21 ขั้นตอน (พร้อมรูปภาพ)

รถโมเดล RC แบบเอียง: โมเดลนี้เป็นรถที่เอียงได้ 1/10 ที่มีล้อหน้าสองล้อและไดรฟ์ด้านหลังหนึ่งอัน ได้มาจากโมเดลไฟฟ้า RC Arrma Vortex 1/10 ซึ่งใช้โครงอะลูมิเนียมและถอดส่วนหลังทั้งหมดออกในตำแหน่งที่เขาวางมอเตอร์ไฟฟ้าและท